<u>"IDPASC School on Frontier</u> <u>Detectors for High Energy</u> and Astroparticle Physics "

Department of Physical Sciences, Earth and Environment - Physics Section - of the University of Siena

#### 2013 Oct 4-6

#### Oct 5, 2013

Advances in 3D silicon sensors

Dr. A.Messineo Università degli Studi di Pisa

alberto.messineo@cern.ch

### Advances in 3D silicon sensors: lecture outline

- Section I

- Introduction and basic principles

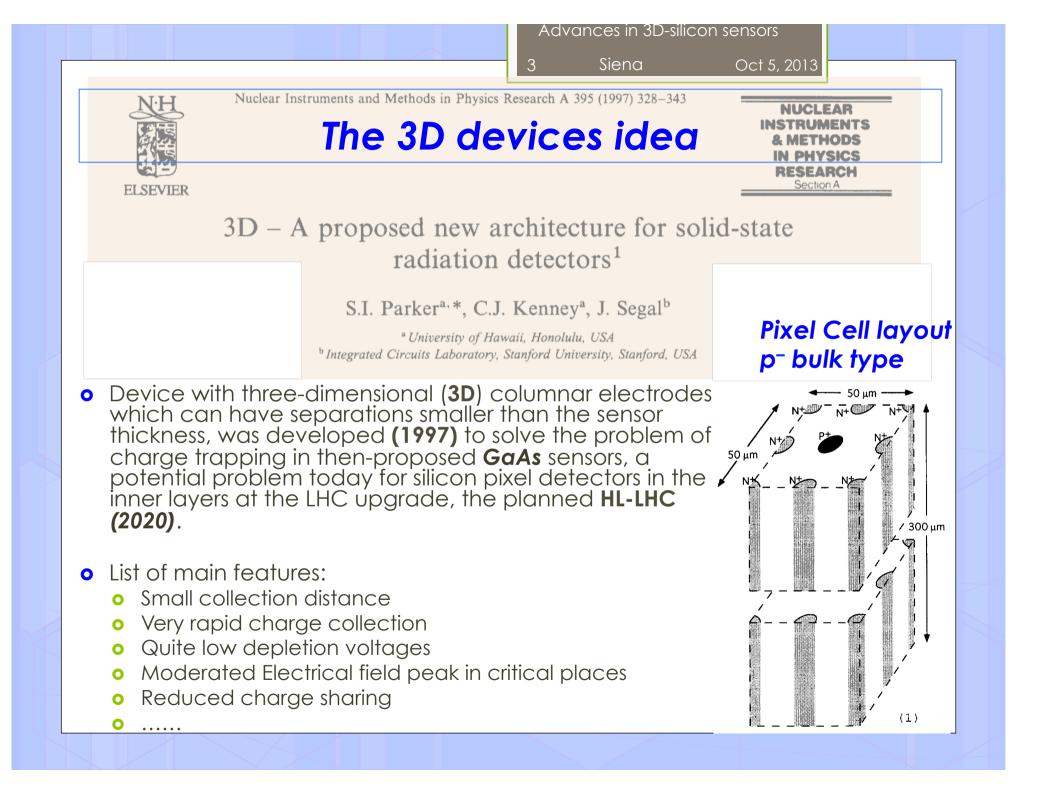

- The 3D devices idea

- Basic features

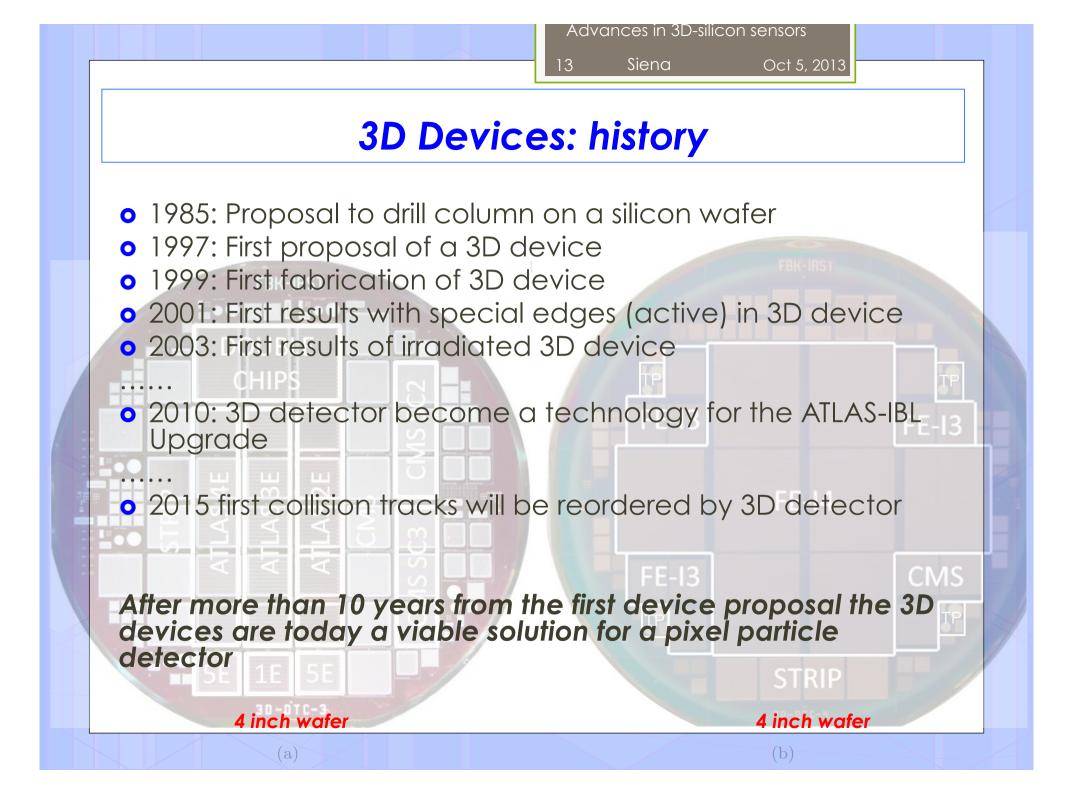

- 3D device history

- Basic technology

- 3D devices performance

- Applications: Examples and Exercises

- Section II

- Advances for future 3D devices

- Process and Layout optimization

- Edge geometrical efficiency

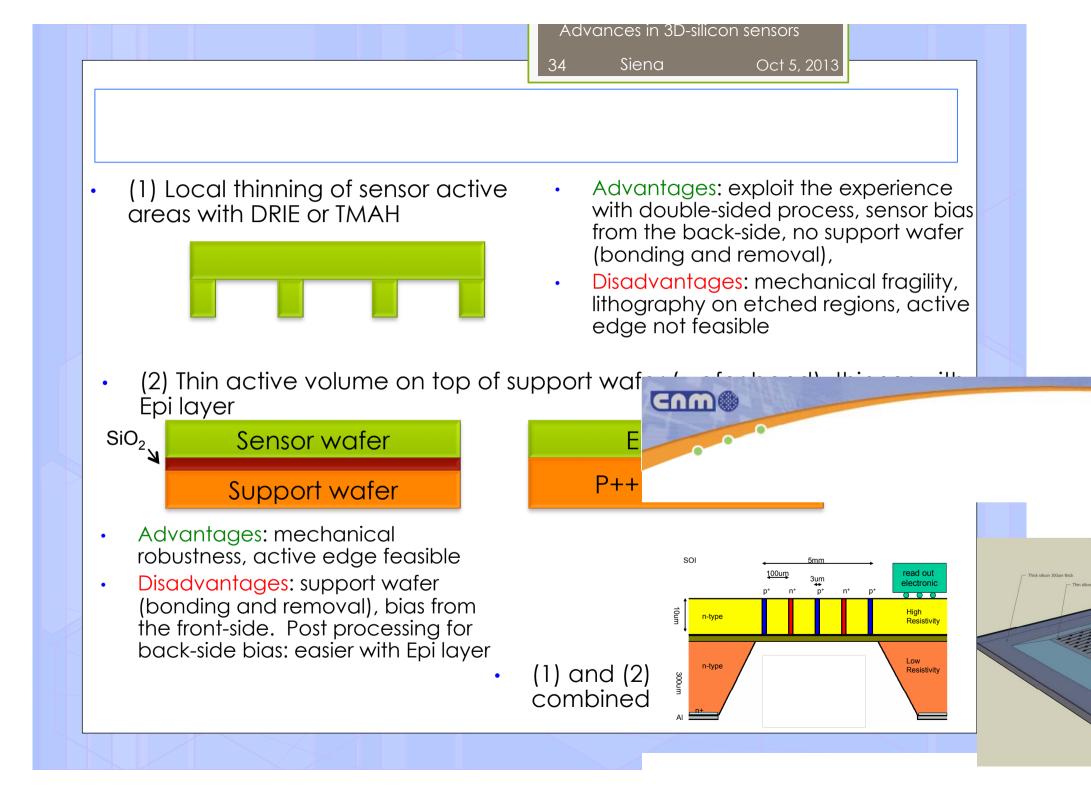

- Thin active region

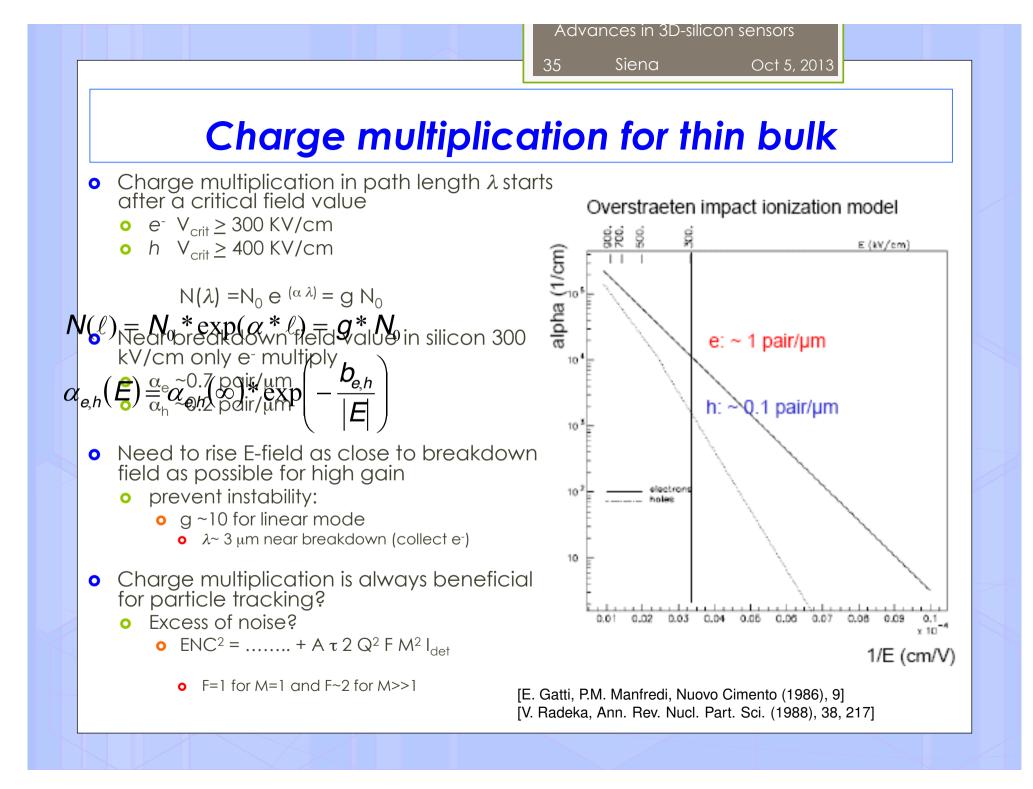

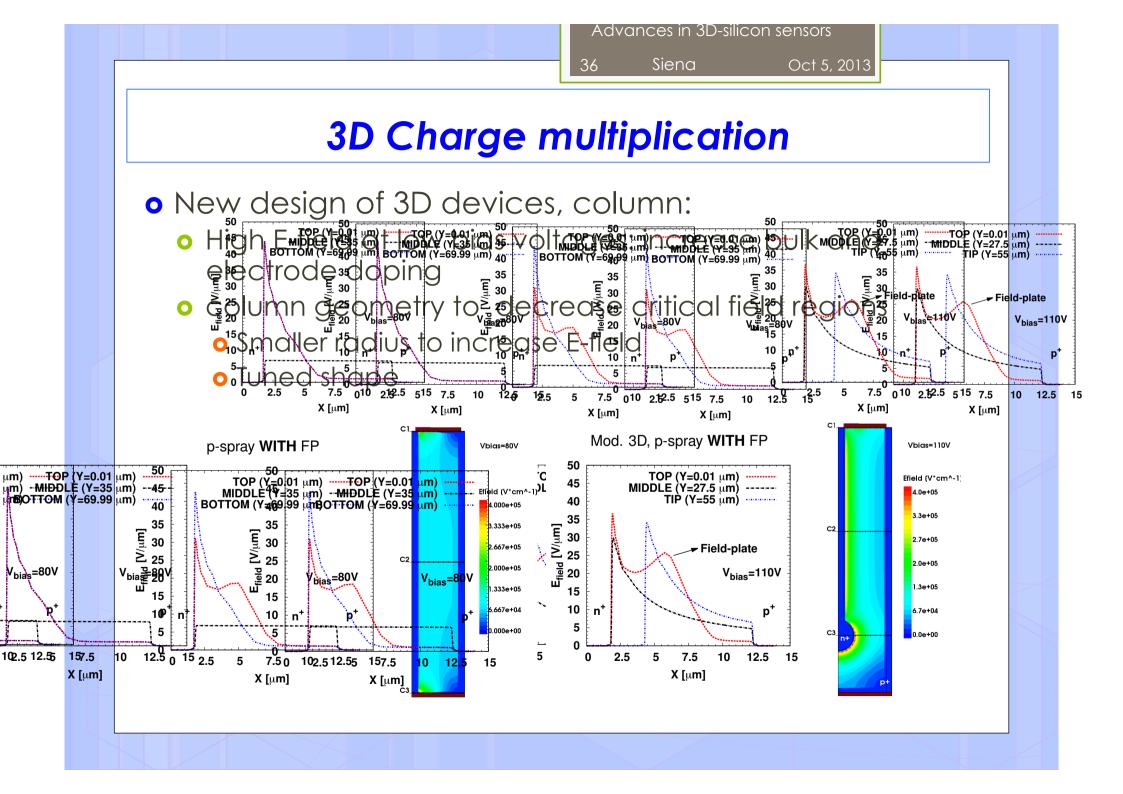

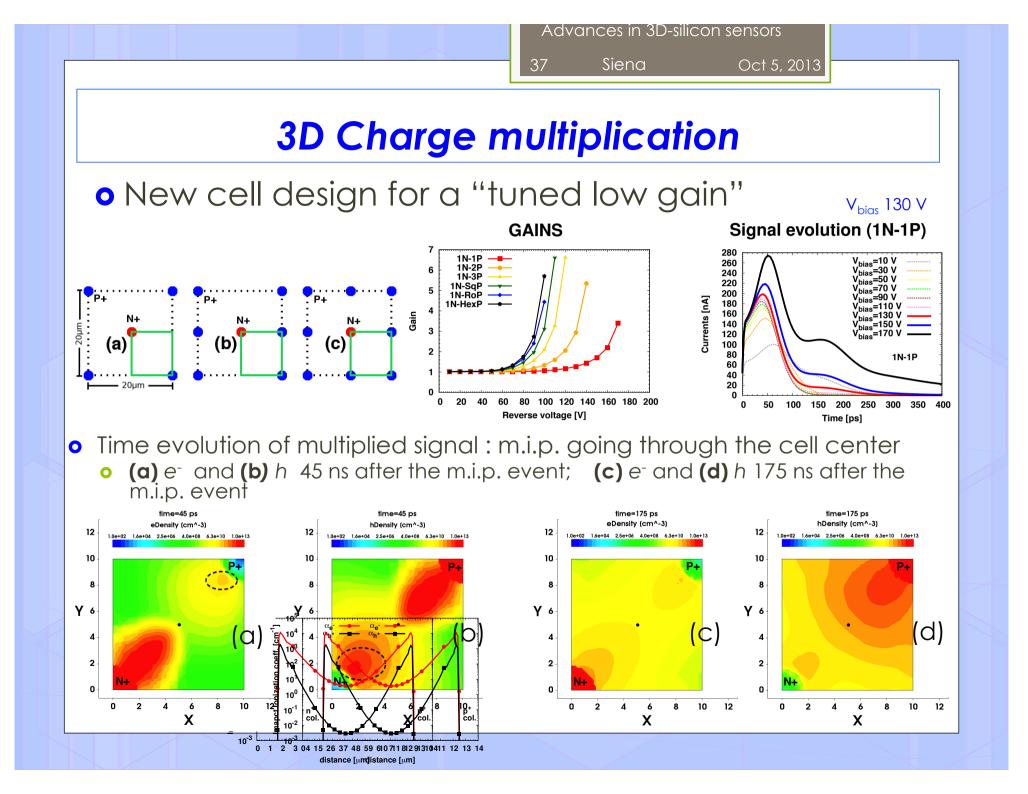

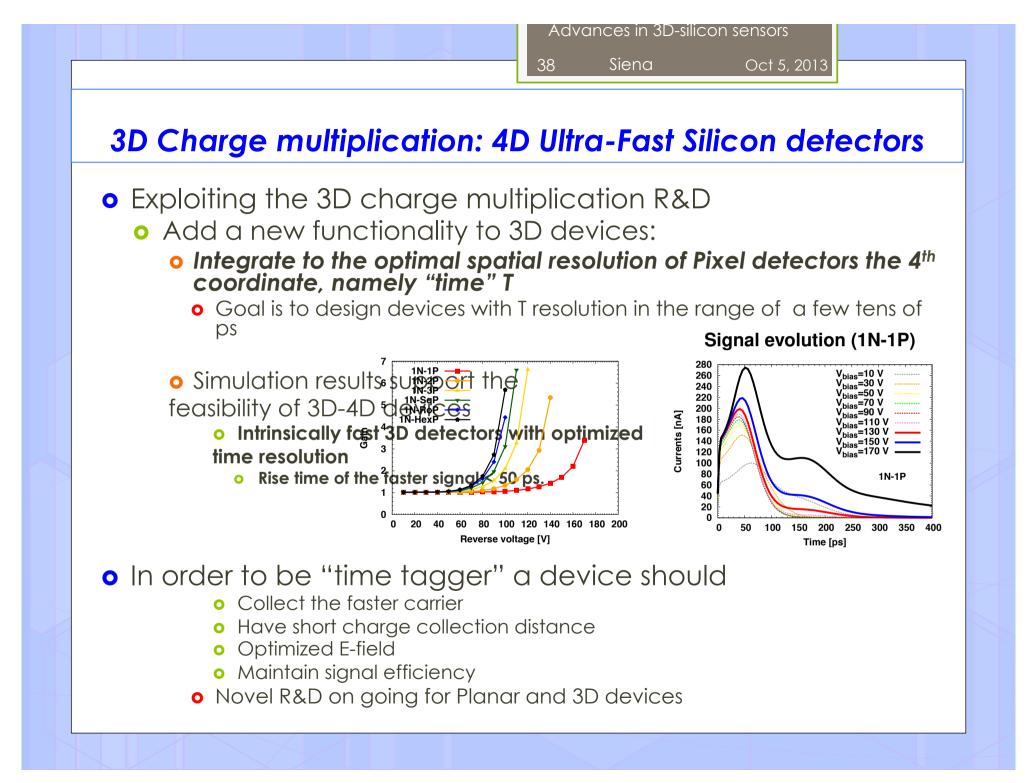

- Charge multiplication and 4D devices

- Applications: Examples and Exercises

- Selected texts: Papers and Books

Section I

Introduction and basic principles

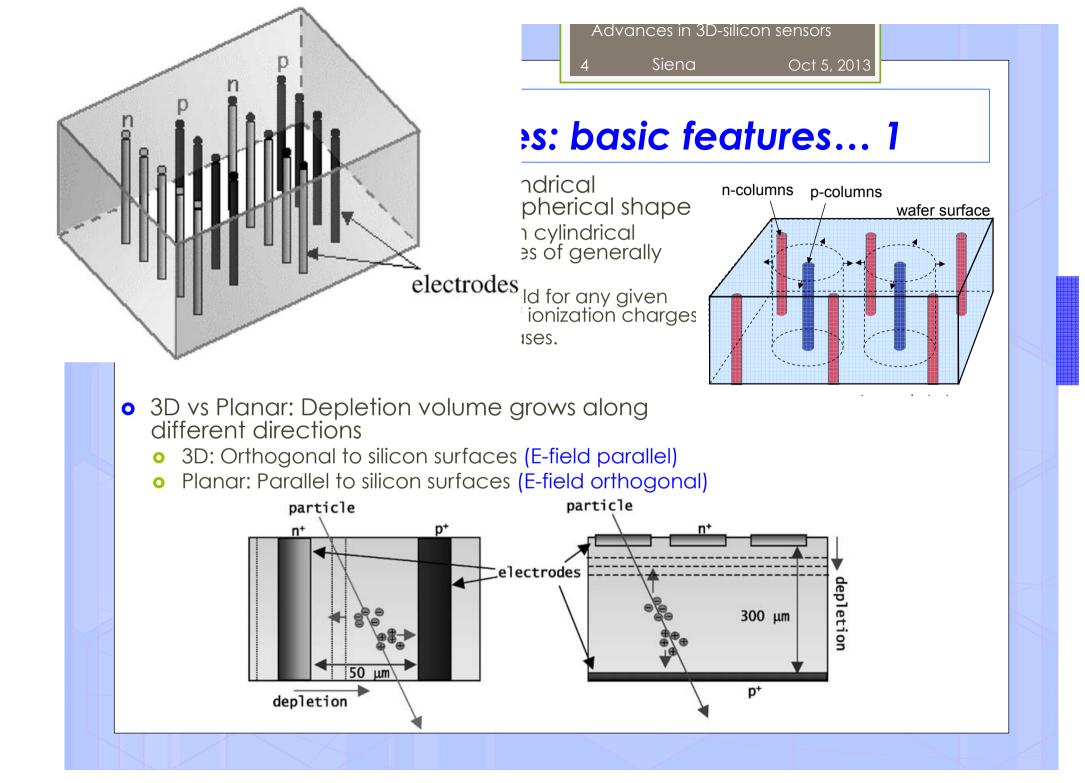

## 3D silicon devices: basic features... 2

5

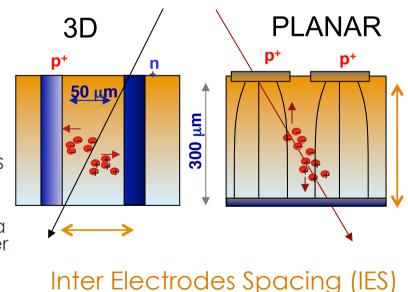

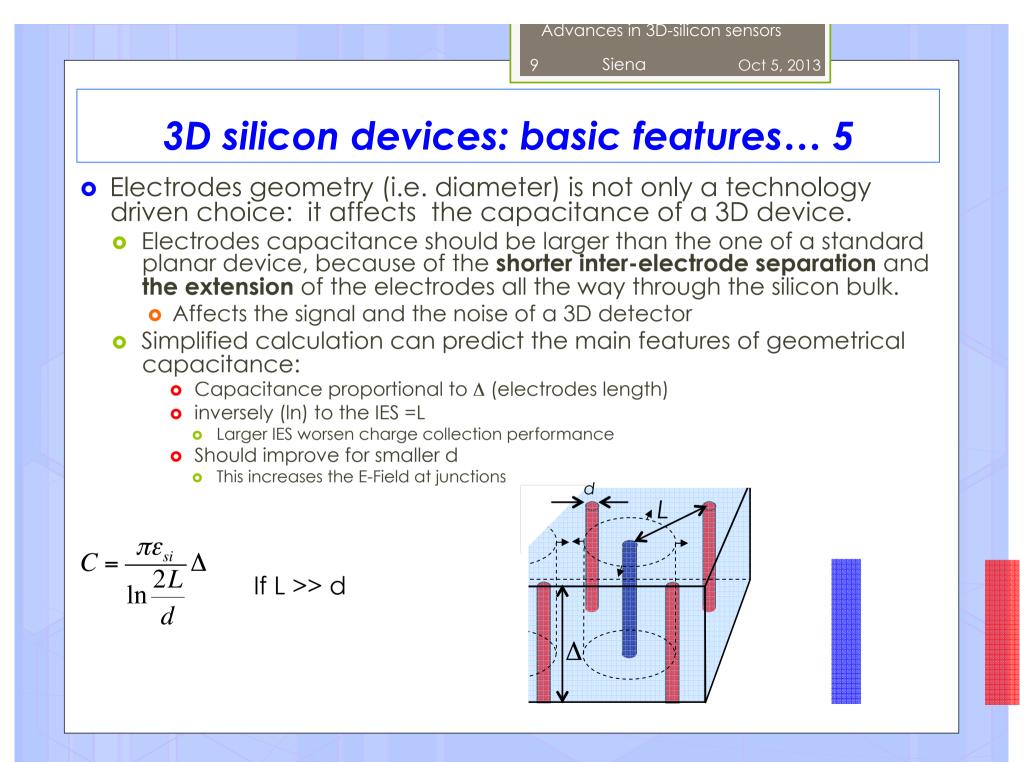

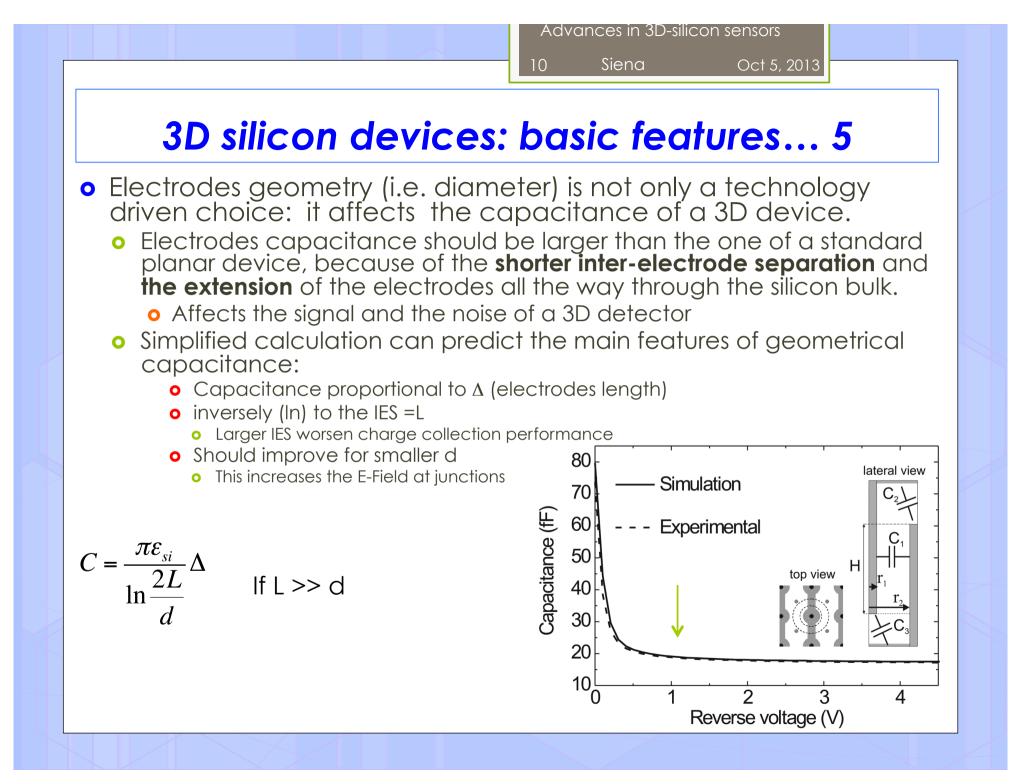

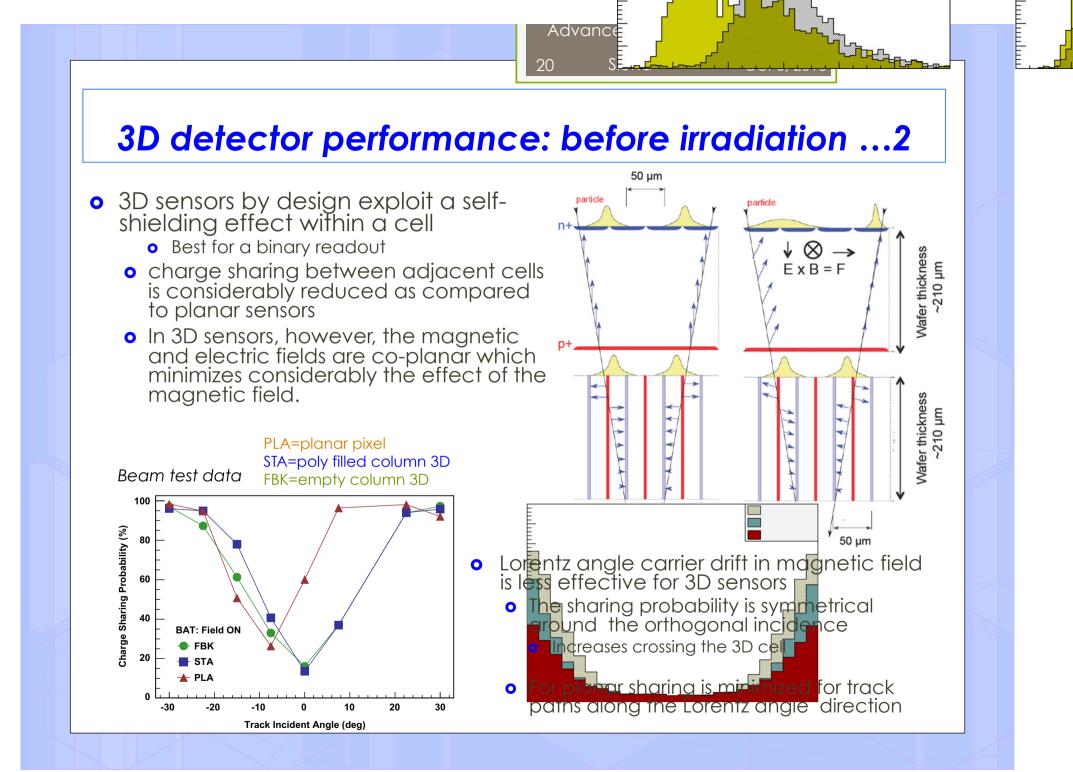

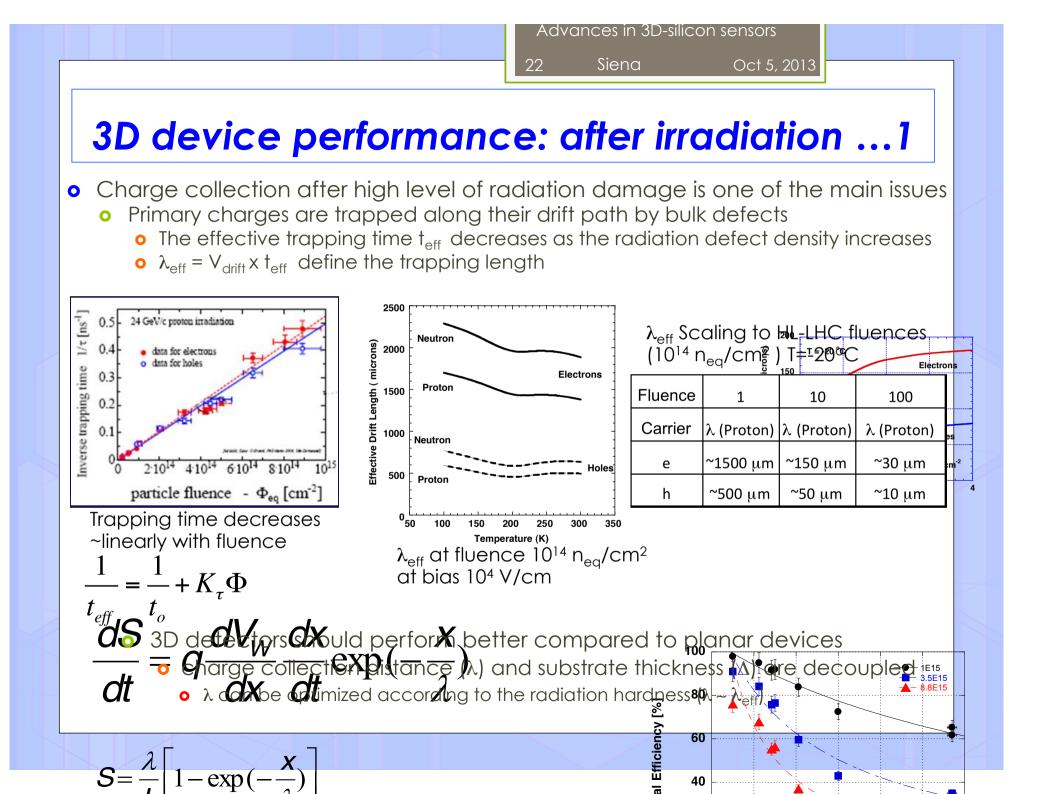

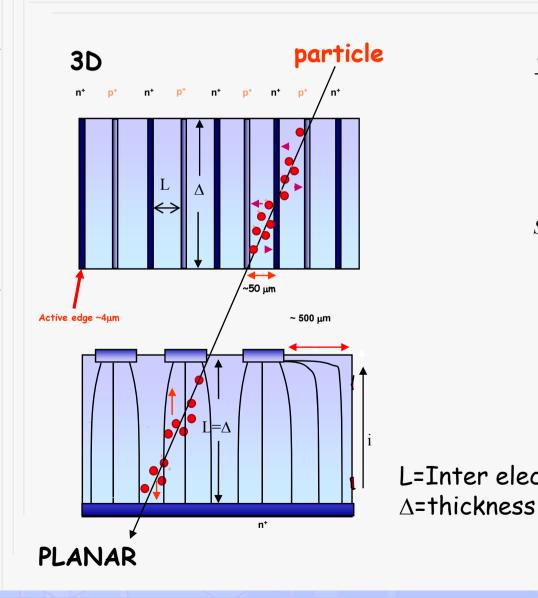

Collection distances (IES) can be as short as 50µm while the charge generated by the traversing particle can have much longer track lengths, depending on the application, by varying the substrate thickness.

(as an example, 24000  $e^-/h$  for a 300-µm-thick silicon substrate)

- Charge collection:

- In a planar detector, each charge along the ionization path is at a different distance with respect to the collecting electrode, so the peak signal induction occurs at different times.

- in a 3D detector the ionization path is parallel to the collecting electrodes. All charges along the path are at almost the same distance from the collecting electrodes. Ignoring some diffusion spreading, the arrival of all the charges is simultaneous, inducing a signal with a faster rise time with smaller spread.

- Ten times faster response compared to a planar structure due to the shorter carrier drift distances.

## 3D silicon devices: basic features... 3

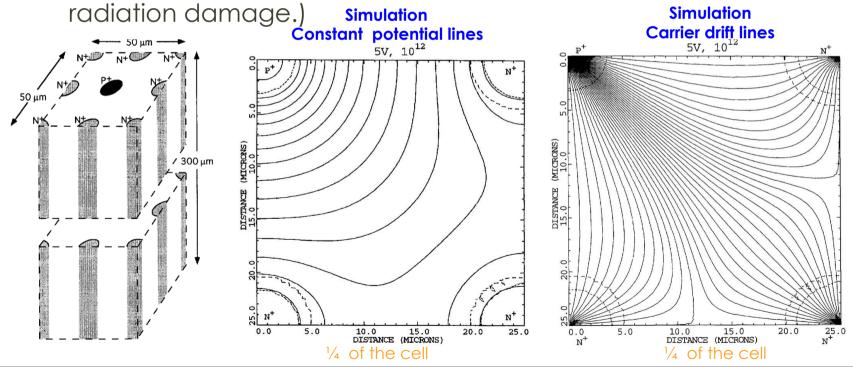

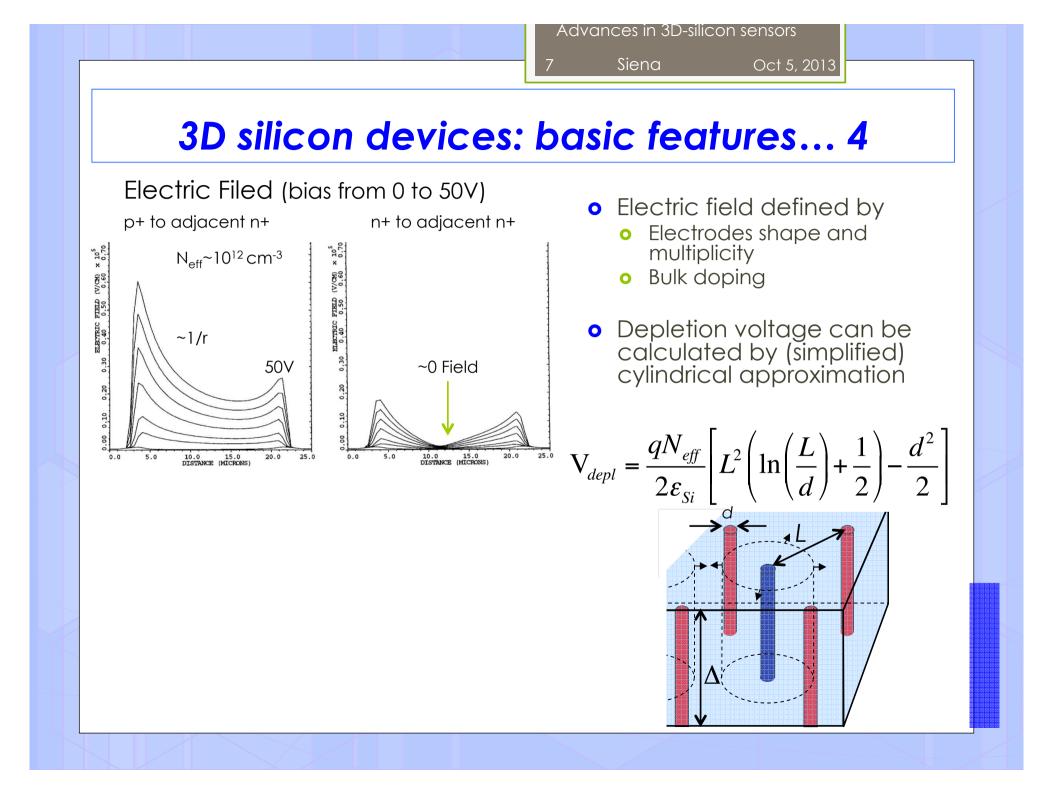

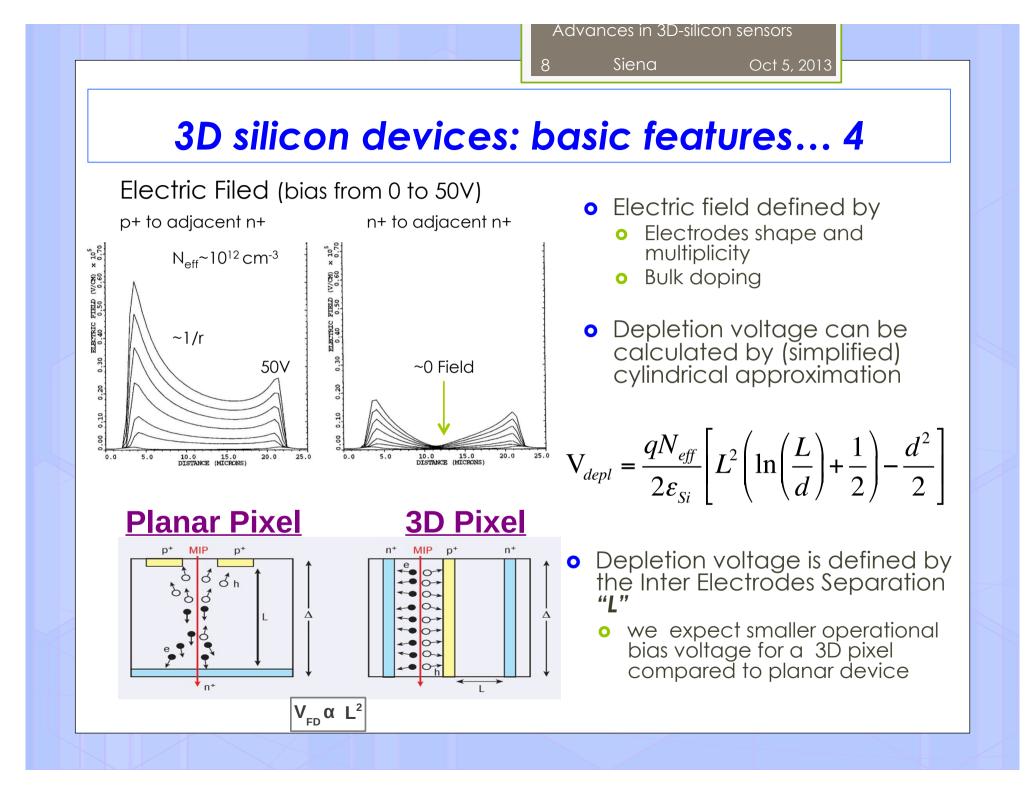

- 3D devices have a non-uniform signal response due to the presence of low/null E-field regions between electrodes of the same doping type, and within the electrodes themselves.

- Charge generated in these regions will initially move by diffusion (slowly), thus increasing the trapping probability (i.e. after

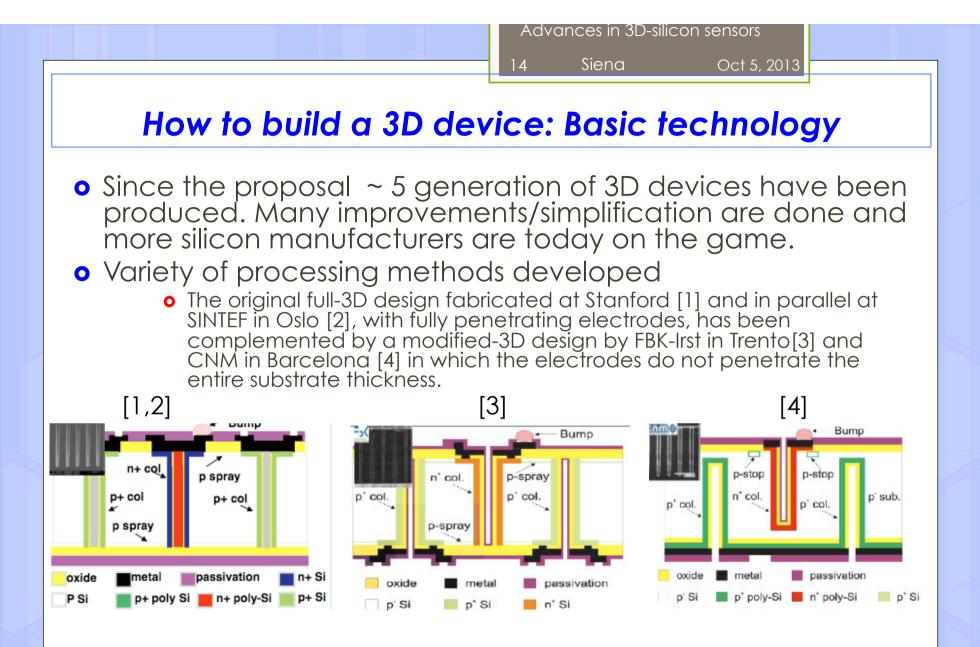

[1] C. Kenney, S. Parker, J. Segal, and C. Storment. IEEE Trans. Nucl. Sci., VOL. 46, NO. 4, AUGUST 1999

[2] T.E. Hansen, et al., J. Instr. 4 (2009) P03010

[3] A. Zoboli, G.F. Dalla Betta, M. Boscardin, C. Piemonte, S. Ronchin, N. Zorzi, L. Bosisio, IEEE Trans. Nucl. Sci. NS-55 (2008) 2775

[4] G. Pellegrini, M. Lozano, M. Ullan, R. Bates, C. Fleta, D. Pennicard, Nucl. Instr. and Meth. A 592 (2008) 38.

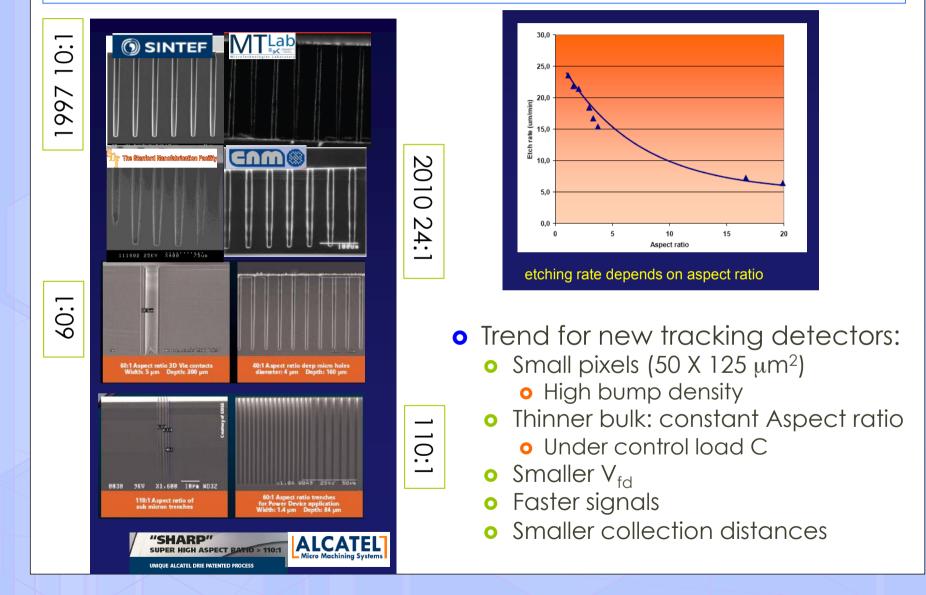

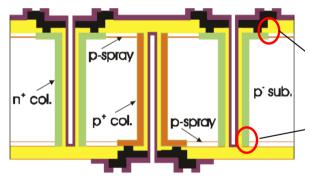

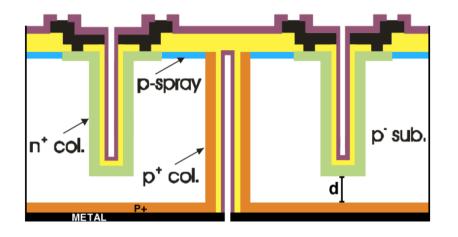

## Oct <u>5, 2013</u> How to build a 3D device: Basic technology

15

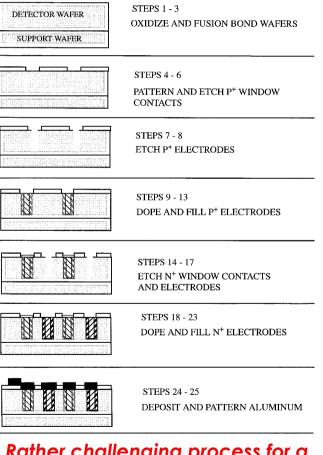

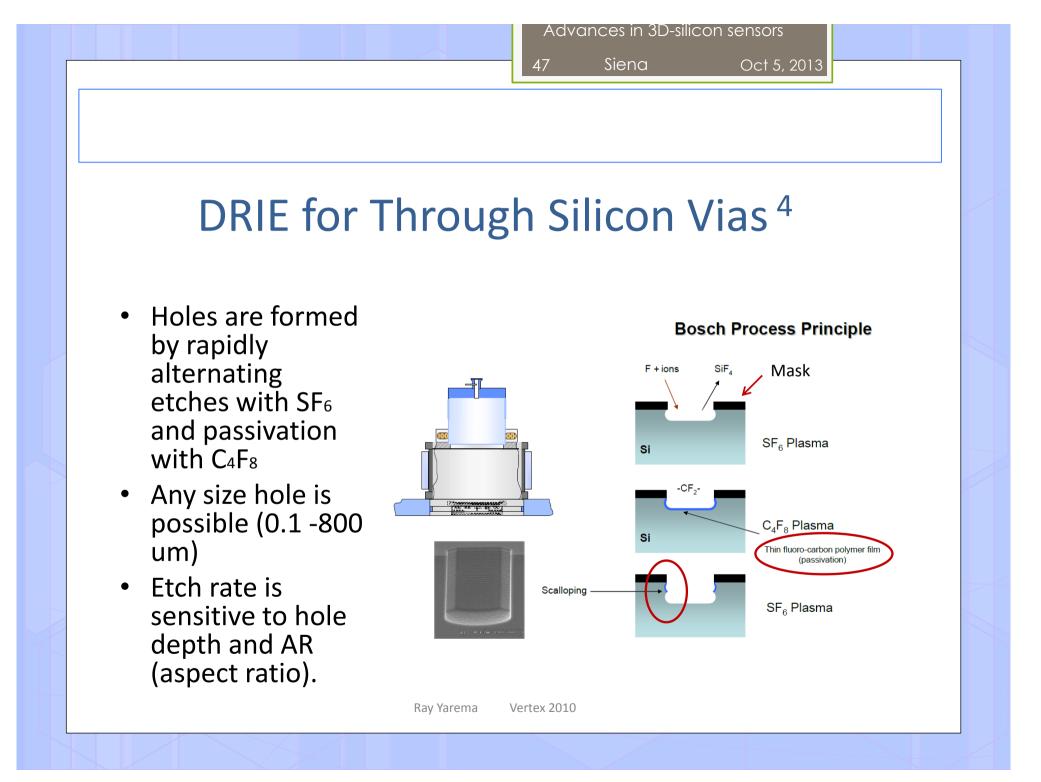

- The fabrication of a 3D device implies process for etching narrow holes with high precision through the silicon bulk.

- First attempt was to build 3D diodes by laser drilling and diffusion [1].

- Today the technology combines 0 micró-machining and standard Very Large Scale Integration (VLŚI) processing

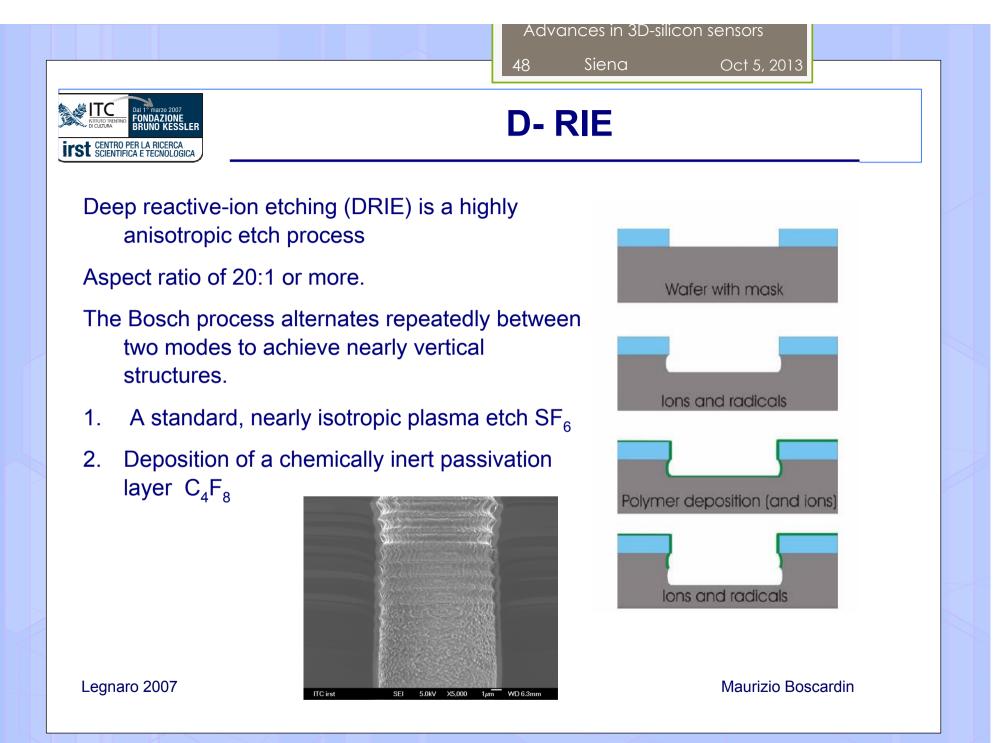

- Optimized solution is by using deep reactive ion etching (DRIE)[2]

- Exploit the high-precision etching techniques in silicon

[1] J. Appl. Phys. 53, 9154 (1982); doi: 10.1063/1.330427 **Deep Reactive Ion Etching** [2] Sensors and Actuators A 144 (2008) 109–116 doi:10.1016/j.sna.2007.12.026

#### TABLE II

Advances in 3D-silicon sensors

Siena

FABRICATION STEPS-SCHEMATIC CROSS SECTION DIAGRAMS. THE DIAGRAMS ARE SHOWN AFTER EACH SET OF STEPS, NEITHER THE WAFERS NOR THE STRUCTURES ARE TO SCALE. THE SUPPORT WAFER WAS THICKER THAN THE DETECTOR WAFER, BUT WITH NO STRUCTURES TO SHOW IT WAS MADE SMALL TO SAVE SPACE

Rather challenging process for a mass production

- both sides

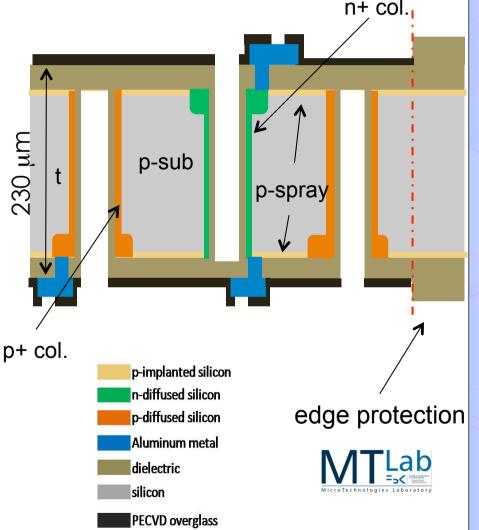

Columns (~12 µm diam )

- Columns (~12 µm diam.)

"empty", doped by thermal

- diffusion and passivated by SiO2

- Poly silicon filled (LPVDC with SiH4)

- Edge protection in order to improve the mechanical yield

- Wafer deformation: critical bow for processing and IV performance

- Aspect ratio: depth to width ratio

- 20

•

•

•

Siena

#### Oct 5, 2013

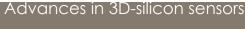

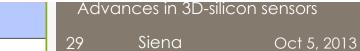

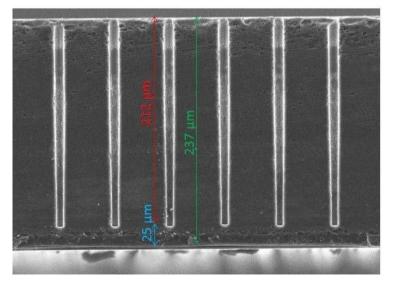

## **3D columns: pictures**

17

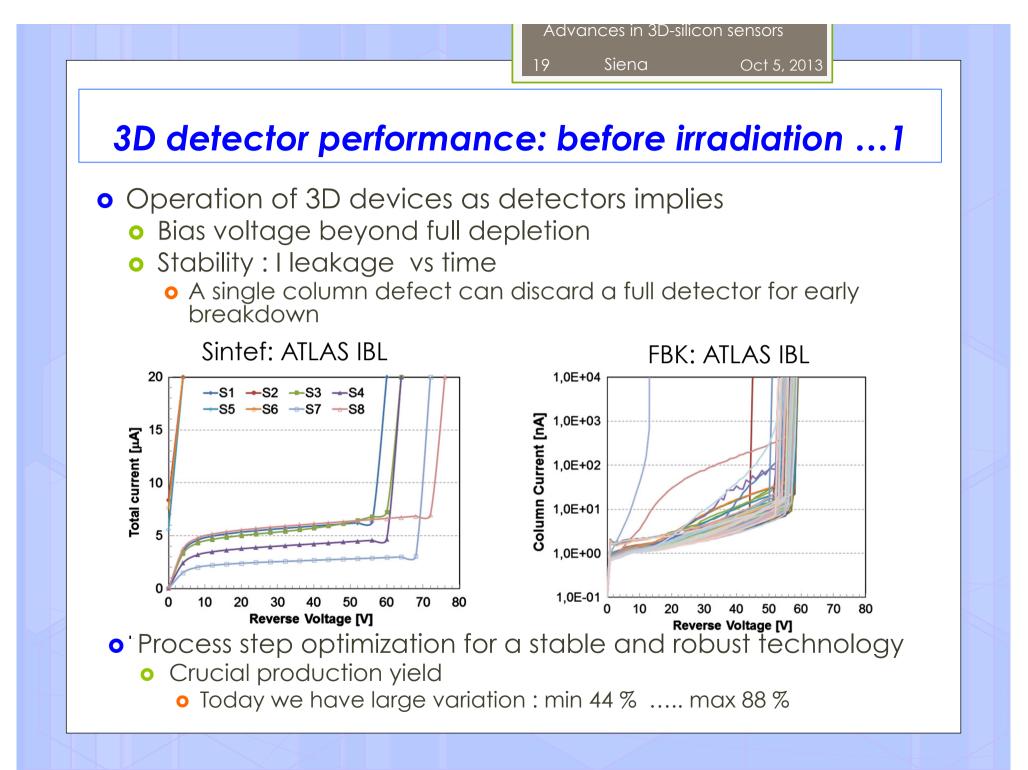

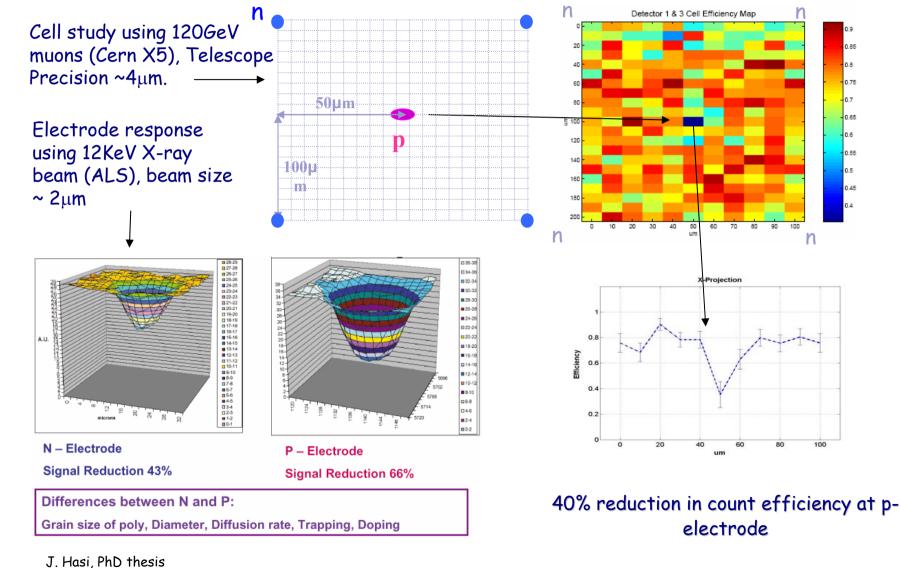

### 3D detector performance: before irradiation ...3

21

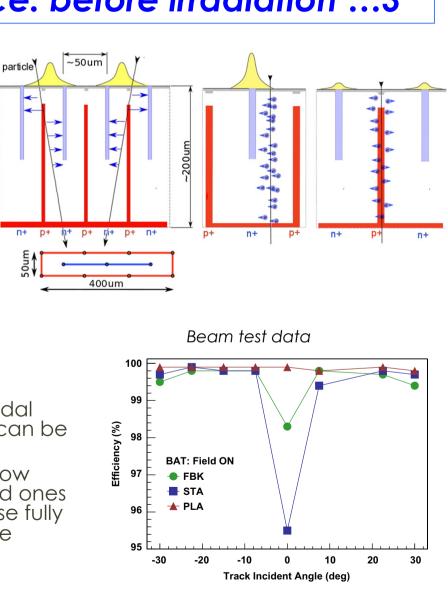

- Tracking efficiency and resolution are fundamental features of pixel detectors.

- Tracking efficiency is defined as the probability of finding a hit close to a track.

- 3D sensors are not 100 % efficient for normal incident tracks: the column volume and the "zero" field regions affect the efficiency

- Given the high aspect ratio of the electrodes, track length inside electrodes is small for inclined tracks, enough charge can be collected in the bulk region to recover efficiency.

- In application to experiment with solenoidal magnetic field the detection efficiency can be recovered, by track curvature:

- 3D empty column electrodes (FBK) show high efficiency, greater than poly filled ones (STA): the electrodes penetrate/diffuse fully the sensor bulk volume decreasing the collection volume size.

Oct 5, 2013

Advances in 3D-silicon sensors

Siena

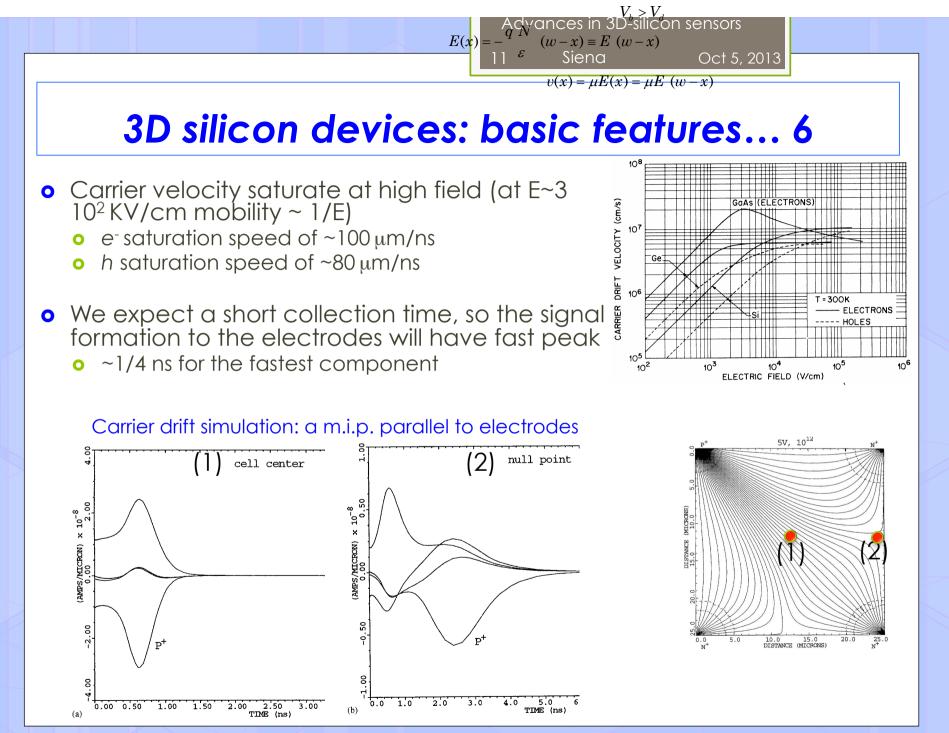

- Calculate maximum time-spread of a m.i.p. within a 3D cell

- Colum electrodes:

- Electrodes can be "empty", poly-silicon or Epitaxial silicon filled

- Discuss pros and cons

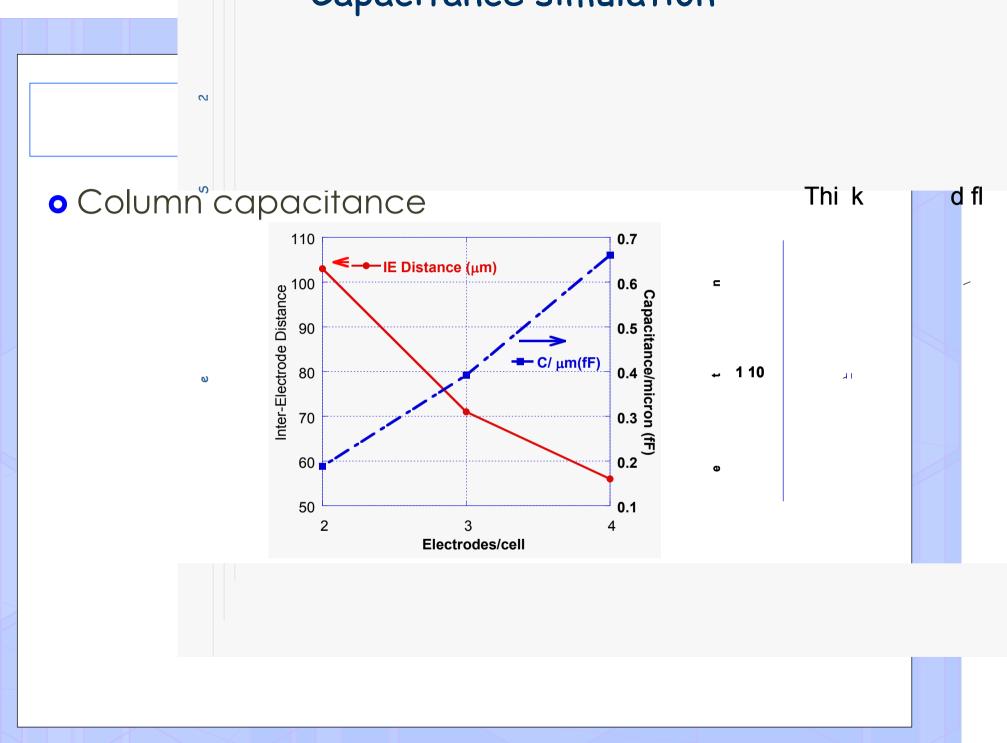

- How much C affect collected signal?

- Measure column capacitance C after radiation damage

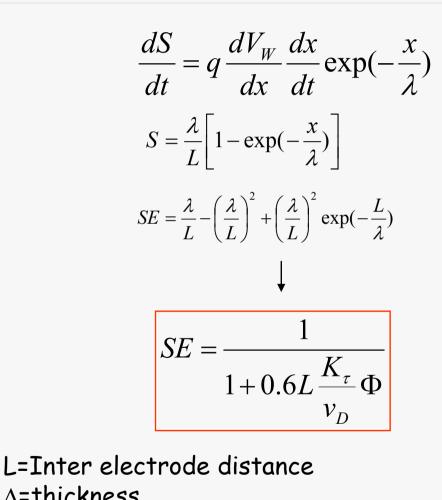

- Derive the approximate expression for

- Depletion voltage

- Signal Efficiency

- 3D pixel efficiency vs collection distance

- Calculate maximal IES admissible

- Derive SE formula after radiation damage

Section II

Advances for future radiation tolerant devices

Siena

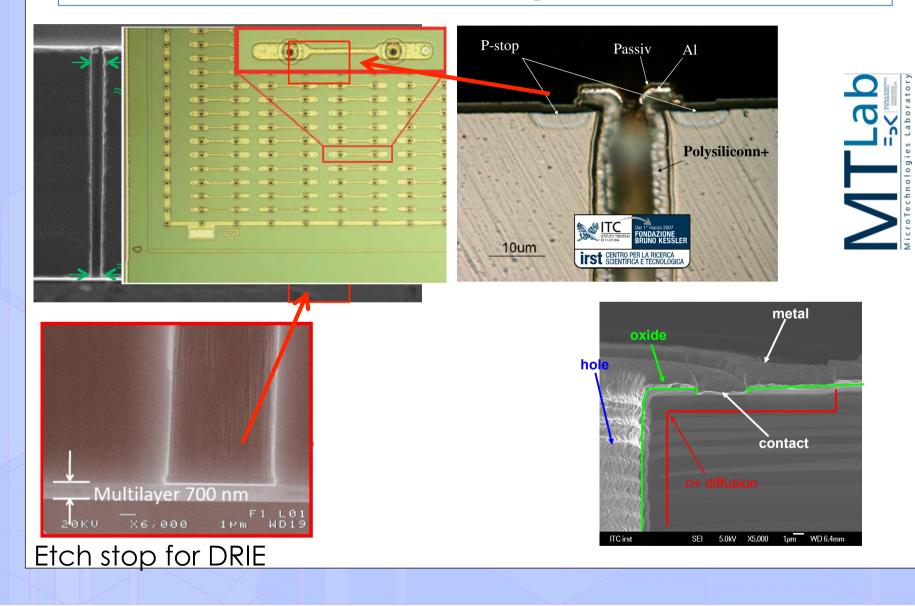

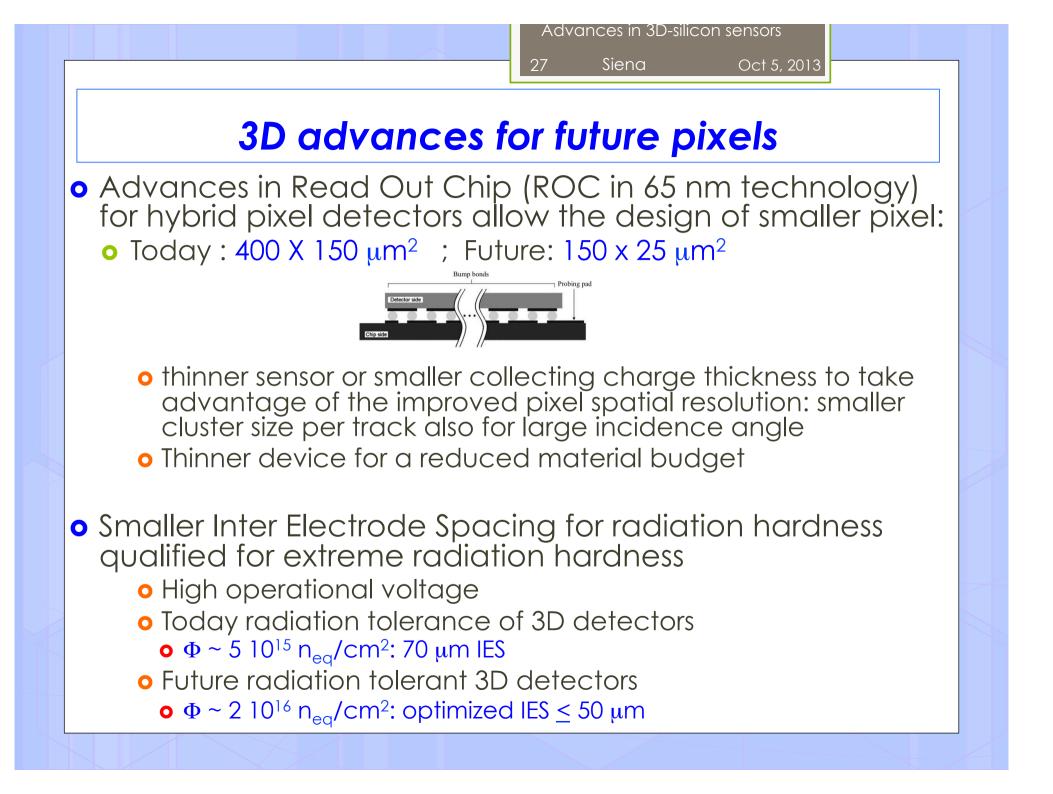

## 3D advances for future pixels

#### • Implications:

- Higher column density and bump density

- o Narrower electrodes are needed

- decrease geometrical inefficiency of electrodes and lower capacitance (noise)

- Thinner substrate allow to maintain constant Aspect ratio and to decrease the capacitance

- Thin electrodes in thin substrate can be easily filled with Poly silicon , increasing the column efficiency

- More readout electrodes connected to the same ROC channel.

# • Sensor thickness to be optimized (depending on signal/threshold)

- o case 1 ~ 150  $\mu$ m: feasible with "passive" sensor

- case 2 < 100  $\mu$ m: charge multiplication necessary

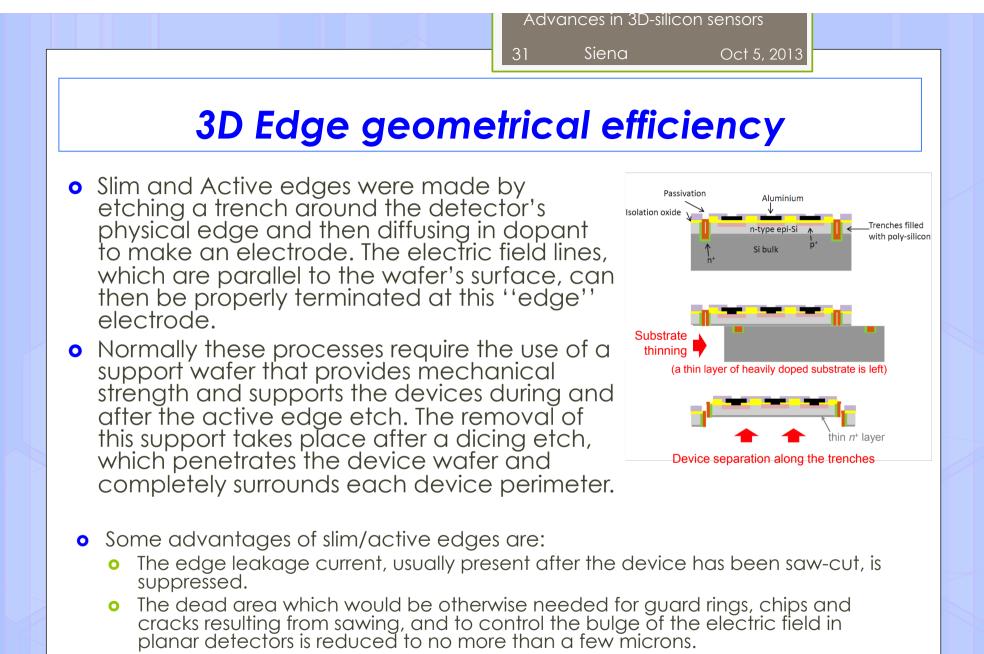

• Very slim (or active) edges for hermetic coverage

#### 3D Process and Layout: DRIE and Aspect (depth/width) ratio

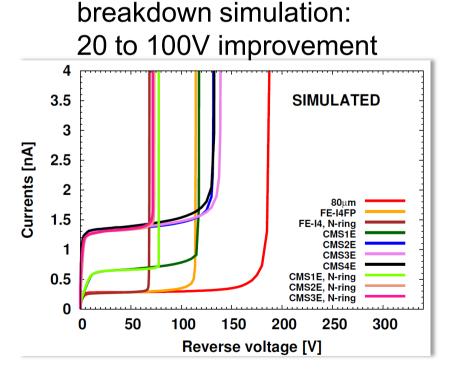

## **3D Process and Layout: design optimization**

- Relatively low intrinsic breakdown voltage • (p-spray related, well understood)

- Might be an issue for post irradiation performance •

- High sensitivity to process defect (a single defect • kills an entire sensor)

- High yield variability •

Simplified process seems promising: significant • improvement on breakdown voltage

• 3D devices have a sort of "by design" protection provided by the column and electric field intrinsically parallel to the wafer surface

- (2) 3D Single sided process

- (3) Robust as (2) with option of single/double sided process as (1)

### **Examples and exercises**

- Seems that increasing electrode density is a beneficial strategy.

- Discuss if for a hybrid pixel 3D detector with pitch size smaller than ROC size, more readout electrodes per pixel, could be drawbacks.

- Design the geometry of a 4D pixel detector

- Compare Planar with 3D design

- Consider: bulk thickness, load C, signal size and "real" signal threshold, S/N, safe multiplication gain, collection time, .....

- Compare performance for the two solutions

• G.Lutz : Semiconductor radiation detectors, Device Physics, Springer 1999

#### Advances in 3D-silicon sensors

42 Siena

Oct 5, 2013

### Papers & PhD thesis & Workshops

- IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 55, NO. 5, OCTOBER 2008, 2775

- Nuclear Instruments and Methods in Physics Research A 587 (2008) 243–249

- Nuclear Instruments and Methods in Physics Research A 694 (2012) 321–330

- IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 48, NO. 5, OCTOBER 2001

- Nuclear Instruments and Methods in Physics Research A 501 (2003) 138–145

- Nuclear Instruments and Methods in Physics Research A 509 (2003) 86–91

- Nuclear Instruments and Methods in Physics Research A 560 (2006) 127–130

- Nuclear Instruments and Methods in Physics Research A 650 (2011) 150–157

- Nuclear Instruments and Methods in Physics Research A 549 (2005) 122–125

- Nuclear Instruments and Methods in Physics Research A 638 (2011) 33-40

- Nuclear Instruments and Methods in Physics Research A 659 (2011) 272–281

- 2009 JINST 4 P03010 (<u>http://iopscience.iop.org/1748-0221/4/03/P03010</u>)

- Nuclear Instruments and Methods in Physics Research A 579 (2007) 642–647

- Link to interesting workshops

- http://rd50.web.cern.ch/rd50/

- http://tredi2013.fbk.eu/

- PhD thesis

- Angela Kok, BRUNEL UNIVERSITY

- M. Povoli, DISI University of Trento

- G. Douglas Stewart, University of Glasgow

- D. Bassignana, Universidad Autonoma de Barcelona

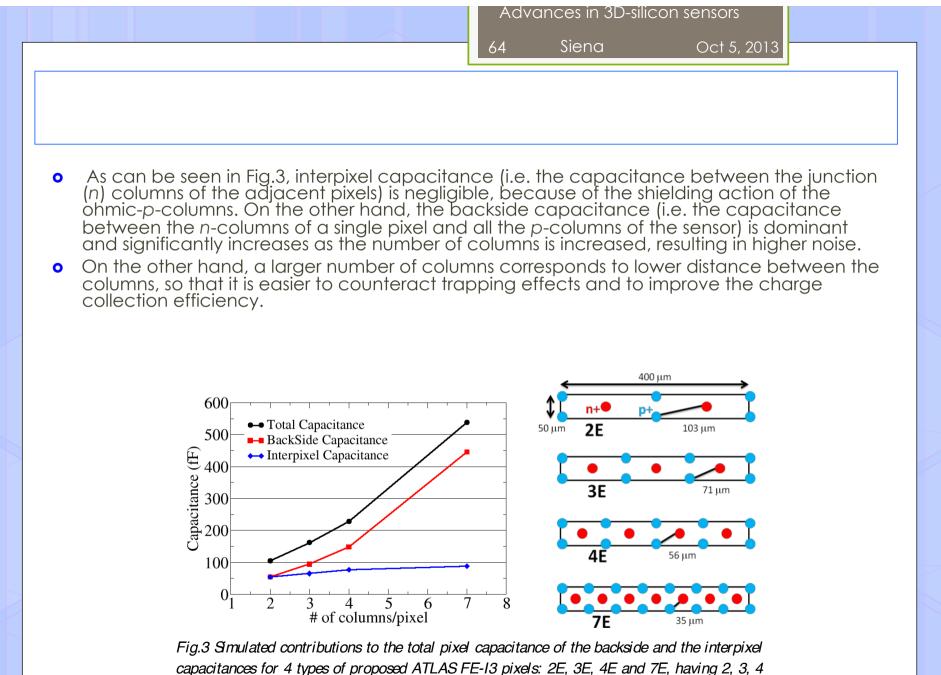

#### cupacitance simulation

### Can 4D-UFSD work? Correct Collected Charge

## Collection time = thickness/ $v_{sat}$ ( $v_{sat}$ = 80 $\mu$ m/ns) (holes) Realistic

resolutio

| Thickness | BackPlane Capacitance |                | Signal    | Coll. Time | Gain required |             | gain & ca        |

|-----------|-----------------------|----------------|-----------|------------|---------------|-------------|------------------|

| [um]      | Pixels [fF]           | Strips [pF/mm] | [# of e-] | [ps]       | for 2000 e    | for 12000 e |                  |

| 1         | 250                   | 5.0            | 35        | 13         | 57            | 343         |                  |

| 2         | 125                   | 2.5            | 80        | 25         | 25            | 149         |                  |

| 5         | 50                    | 1.0            | 235       | 63         | 8.5           | 51          |                  |

| 10        | 25                    | 0.50           | 523       | 125        | 3.8           | 23          |                  |

| 20        | 13                    | 0.25           | 1149      | 250        | 1.7           | 10.4        |                  |

| 100       | 3                     | 0.05           | 6954      | 1250       | 0.29          | 1.7         | Т                |

| 300       | 1                     | 0.02           | 23334     | 3750       | 0.09          | 0.5         | <b>Good time</b> |

For pixel thickness > 5 um, Capacitance to the backplane Cb < Cint (200 fF)

For pixel thickness = 2 um, Cb ~  $\frac{1}{2}$  of Cint, and we might need bipolar (SiGe)?

Viable sensor thickness 2  $\mu$ m – 10  $\mu$ m (i.e. 20-100ps)

Needed Gain: Pixels 4 - 25, Strips (1 mm) 20- 150

(much less than APD's or SiPM)

#### Note: CNM (Barcelona) is routinely producing 10 $\mu$ m thick sensors.

Hartmut F-W/ Sadrozinski LIESD RD50 ARO 2013

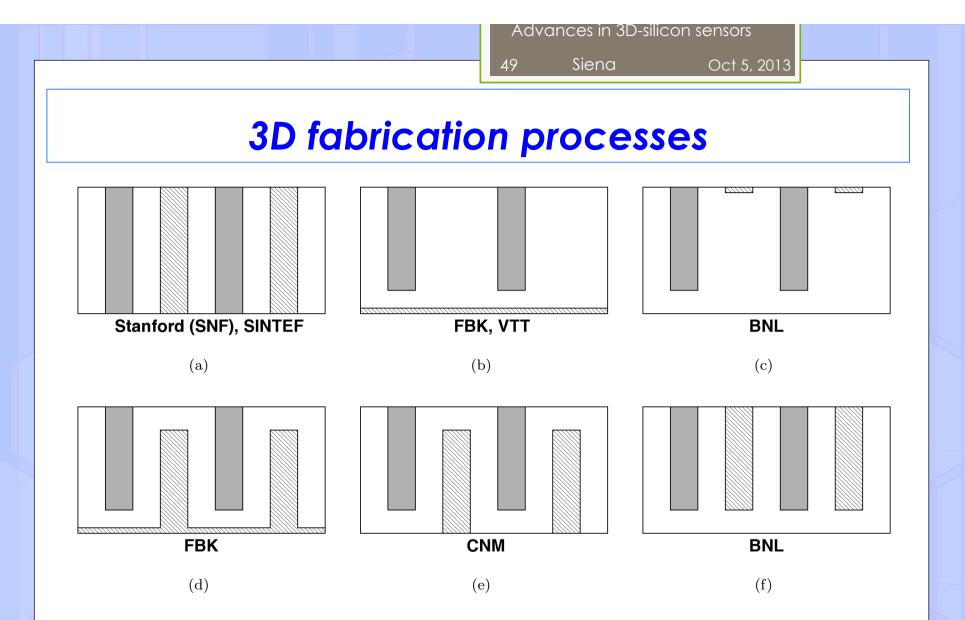

Figure 3.14: Schematic representations of all the proposed approaches to the 3D technology: the original architecture (a) is compared with: Single Type Column implementations from FBK/VTT (b) and BNL (c), Double Sided Double Type Columns from FBK (d) and from CNM (e) and finally the single sided double type column from BNL (e).

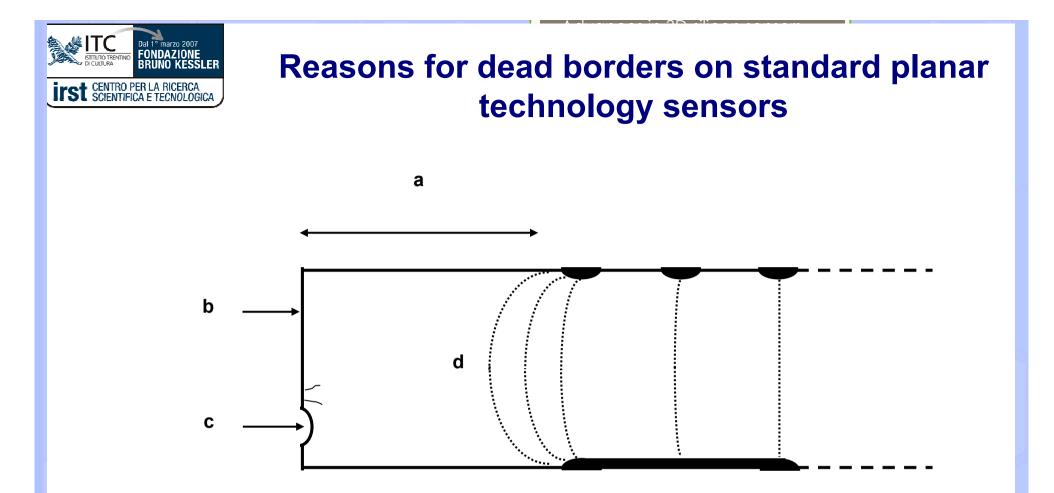

- a. space for guard rings

- b. sawed edges connecting top and bottom are conductors

- c. chips and cracks are also conducting and can reach inside the edges

- d. the field lines bulge out, and should be kept away from b and cs

Maurizio Boscardin

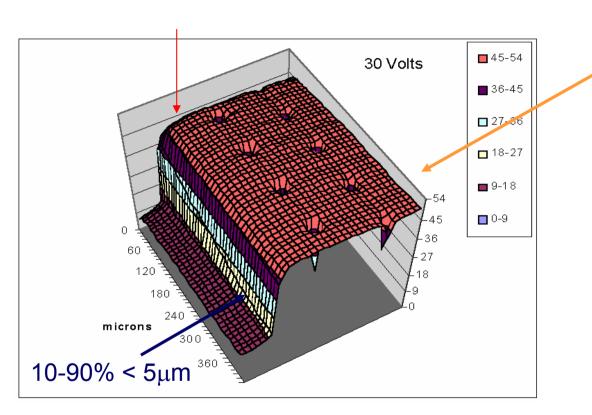

#### 3D edge sensitivity using 13 keV X-rays at Berkeley

X-ray

Measurement Performed using a 2 µm beam

> J. Hasi, C. Kenney, J. Morse, S. Parker

Electrodes ~ 1.8% of total area

X-ray micro-beam scan, in 2  $\mu$ m steps, of a 3D, n bulk and edges, 181  $\mu$ m thick sensor. The left electrodes are p-type Efficiency measured in test beam ~98%

Legnaro 2007

Maurizio Boscardin

# Electrodes area ~1.8% of total area

a a a a in 2D ailia a n

Cinzia Da Via'- Vertex 06 - Perugia - September 2006

Legnaro 2007

Maurizio Boscardin

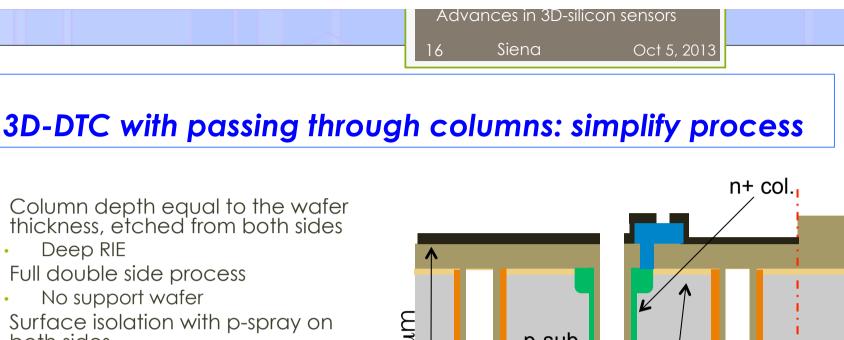

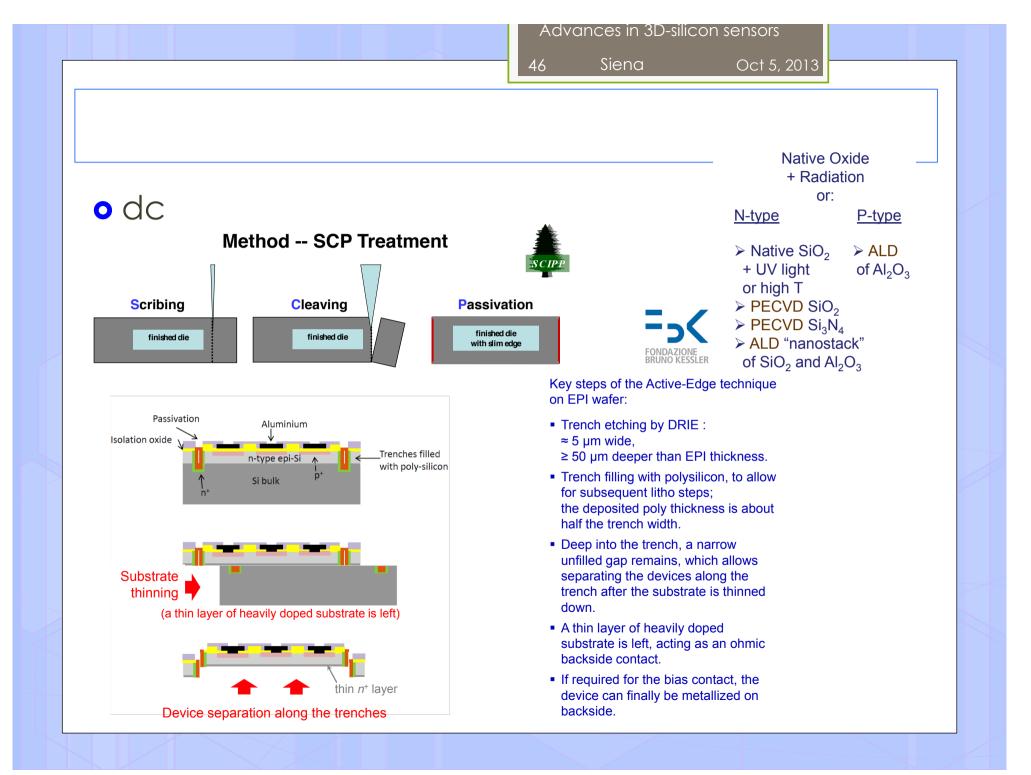

#### New technology

# optimization of the DRIE step to accurately control columns depth

- partially etched junction columns;

- passing-through ohmic columns for effective slim edges

- reduction of back-side masks;

- process simplification.

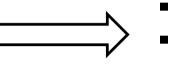

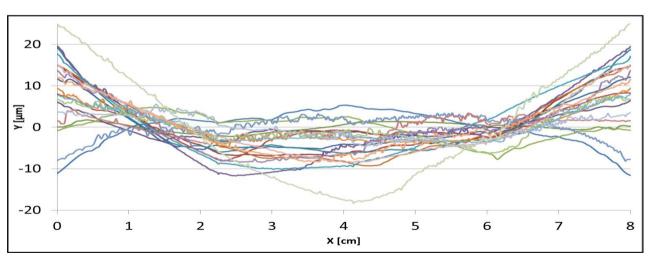

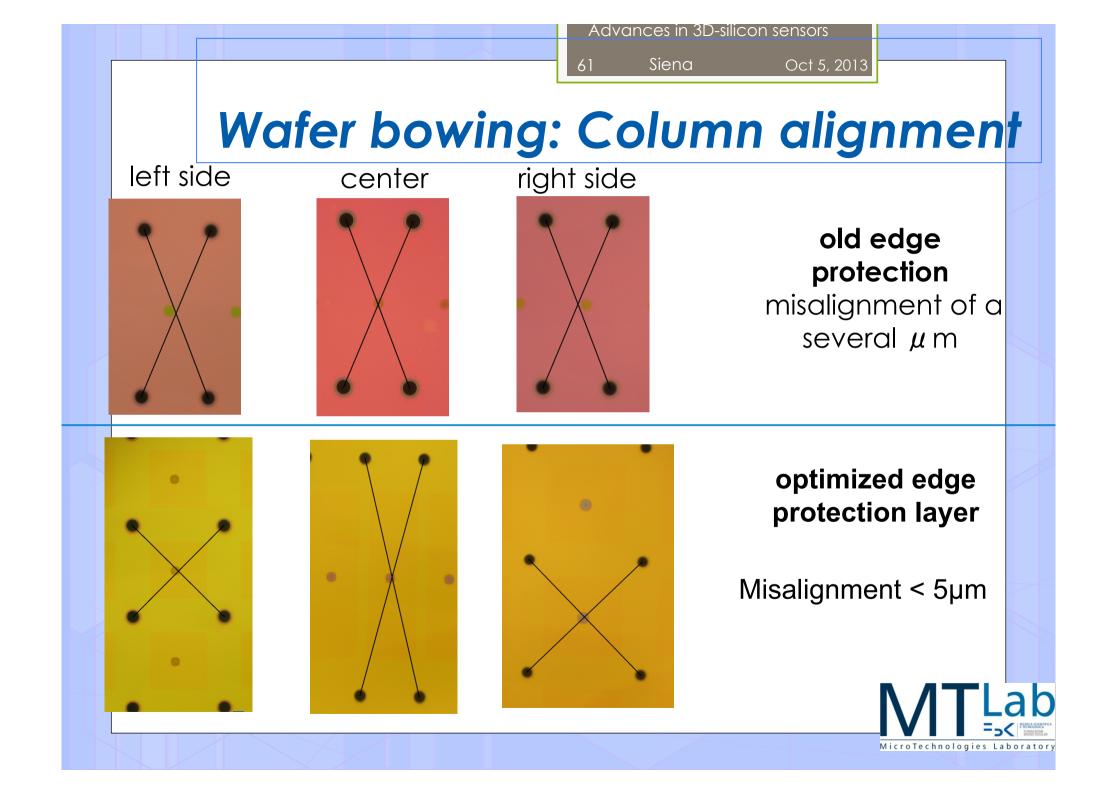

# Optimize edge protection: wafer bowing

Edge protection effects on the wafer bowing.

A high bowing induces

- High leakage current

- Misalignment among columns

- Bonding problem

Old edge protection  $\rightarrow$  wafers warp up to 120  $\mu$ m

**Optimized edge protection**  $\rightarrow$  wafers warp < 30  $\mu$ m

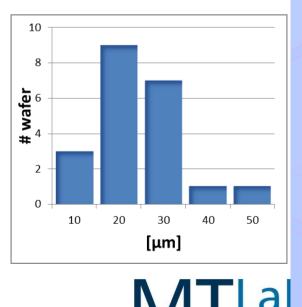

## TRAPPING in Si $\rightarrow$ collect electrons, increase E-field

and USE SHORT 'IES' (THIN SUBSTRATES FOR PLANAR) NIMA 603 (2009) 319-324

FAS

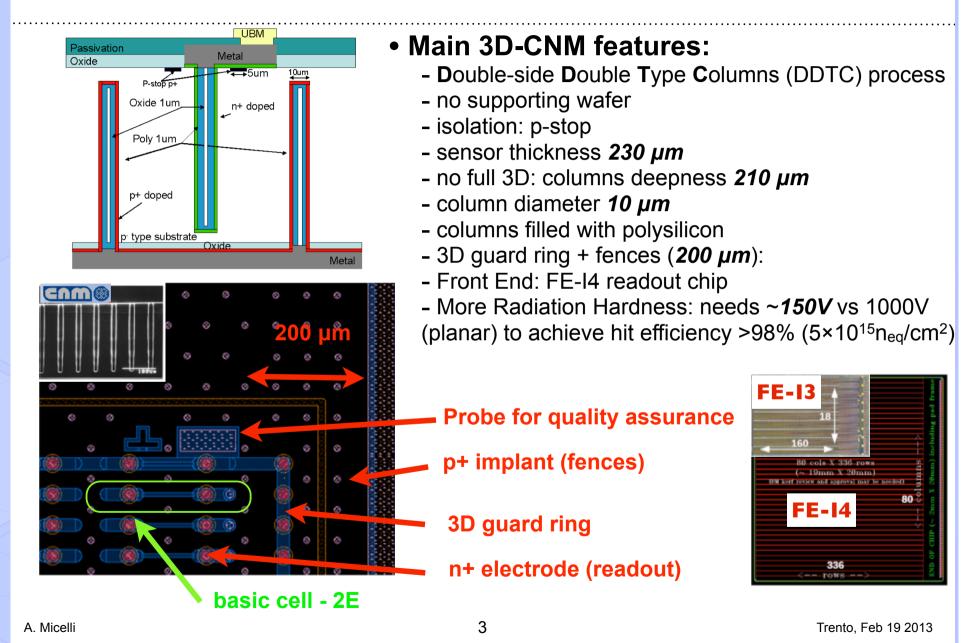

# **3D IBL Production**

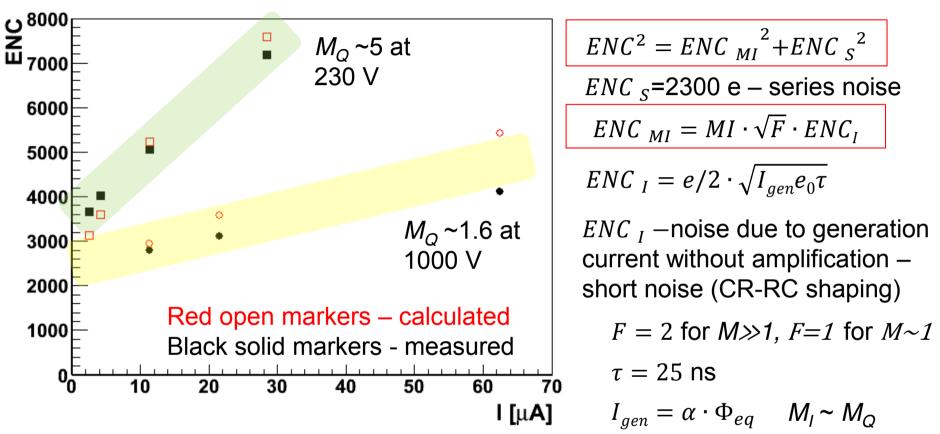

# **Calculation of the noise**

Good agreement between measured and calculated noise.

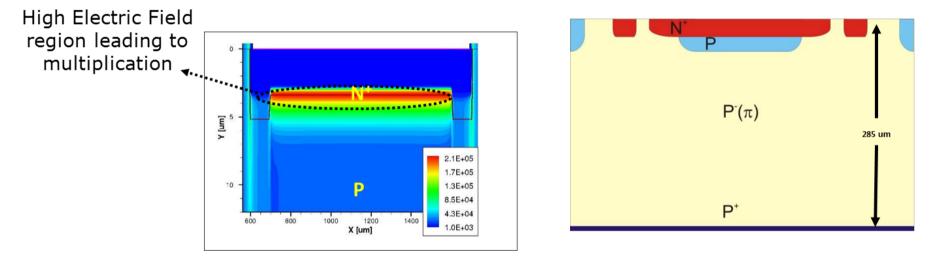

#### 2. Low gain avalanche detectors (LGAD)

Creating a n++/p+/p- junction along the centre of the electrodes. Under reverse bias conditions, a high electric field region is created at this localised region, which can lead to a multiplication mechanism<sup>2</sup>.

<sup>2</sup>P. Fernandez et al, "Simulation of new p-type strip detectors with trench to enhance the charge multiplication effect in the n-type electrodes", Nuclear Instruments and Methods in Physics Research A658 (2011) 98–102.

8 / 29

59 Siena

Oct 5, 2013

# **Optimize edge protection**

#### Table 4

Summary of the yield on selected wafers from the first productions batches.

|                                         | wafers Total sensors | Good sense | ors Yield (%) |

|-----------------------------------------|----------------------|------------|---------------|

| FBK-A1012FBK-A11(*)4CNM118CNM215Total49 | 96                   | 58         | 60.4          |

|                                         | 32                   | 14         | 43.7          |

|                                         | 144                  | 86         | 59.7          |

|                                         | 120                  | 85         | 70.8          |

|                                         | 392                  | 243        | 62.0          |

Mechanical fragility of wafers manly due to a cracks on the wafer edge caused by D-RIE etch step:

✓ Need a special edge protection during DRIE etching (electrostatic clamping) to prevent the creation of cracks that could cause the breakage during the processing.

$\checkmark$  Need a special care during processing

# Mechanical yield with the optimized edge protection:

|             | initial | broken | mechanica |  |  |  |

|-------------|---------|--------|-----------|--|--|--|

|             | wafers  | wafers | yield (%) |  |  |  |

| 3D ATLAS 10 | 25      | 5      | 80%       |  |  |  |

| 3D ATLAS 11 | 25      | 3      | 88%       |  |  |  |

| 3D ATLAS 12 | 23      | 6      | 74%       |  |  |  |

| 3D ATLAS 13 | 20      | 8      | 60%       |  |  |  |

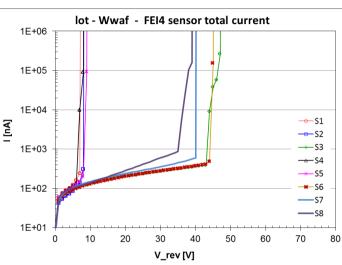

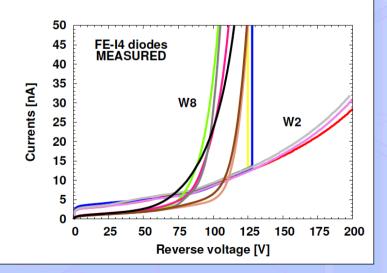

# Wafer bowing: leakage current

60

The wafer bowing strongly influences the leakage current.

With the optimized edge protection it is reduced of one order of magnitude.

Leakage current on planar test diodes (4mm<sup>2</sup>)

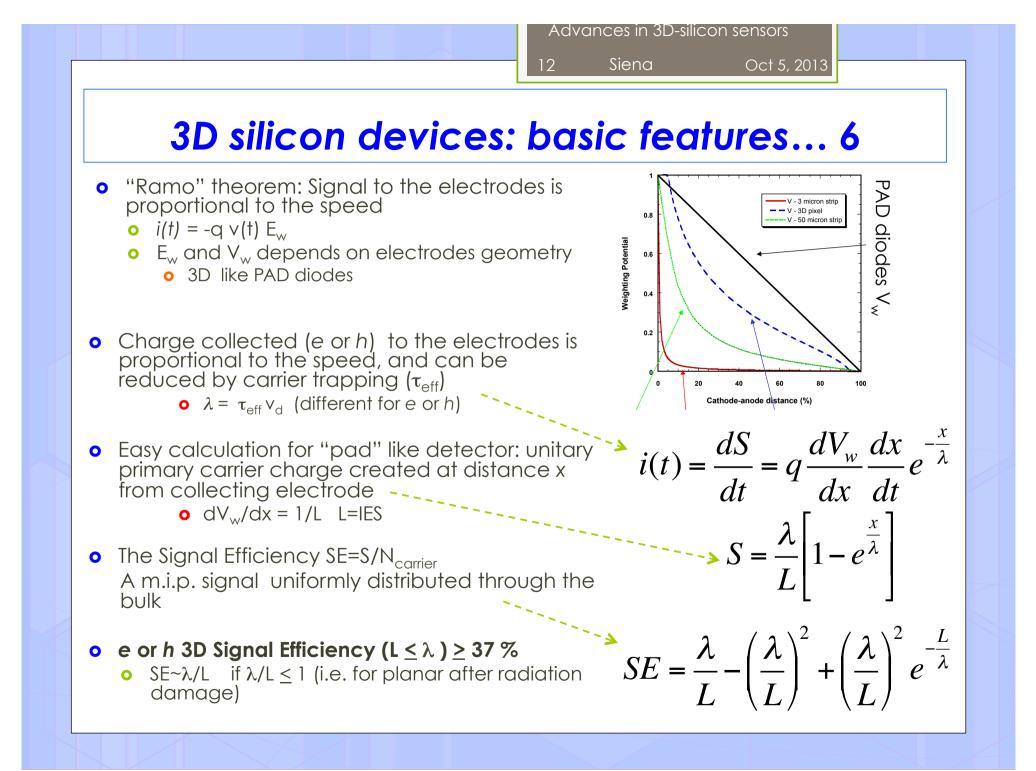

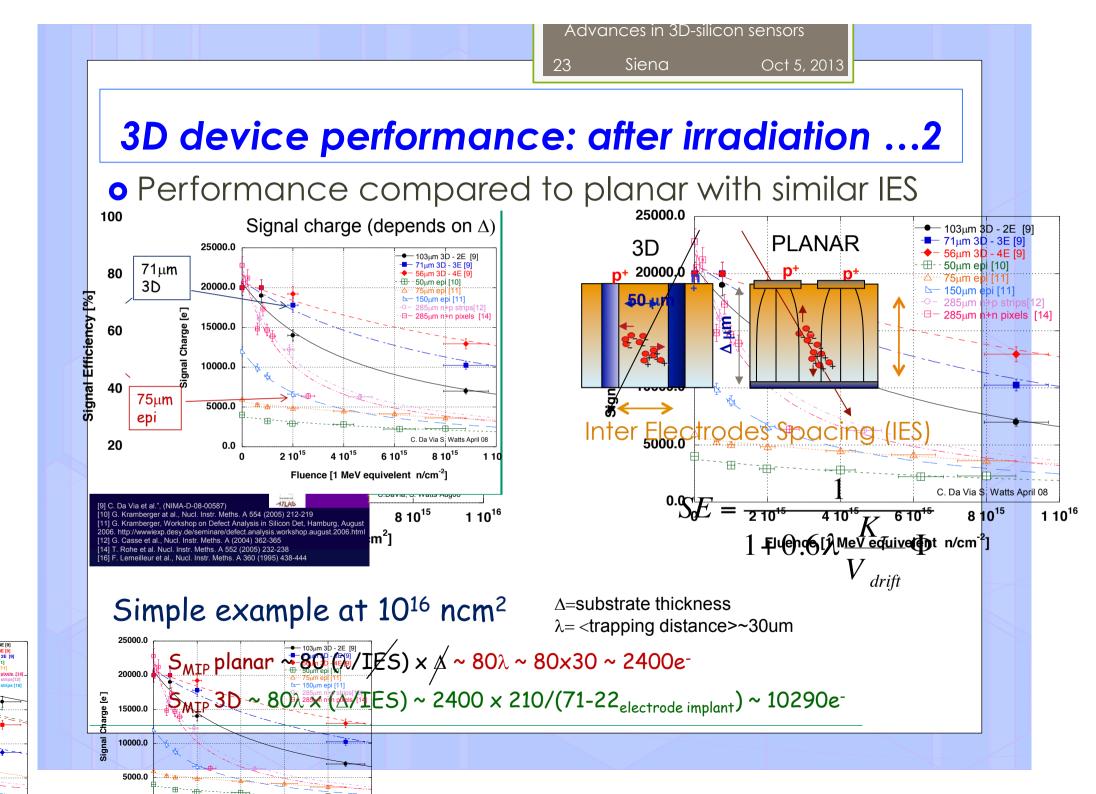

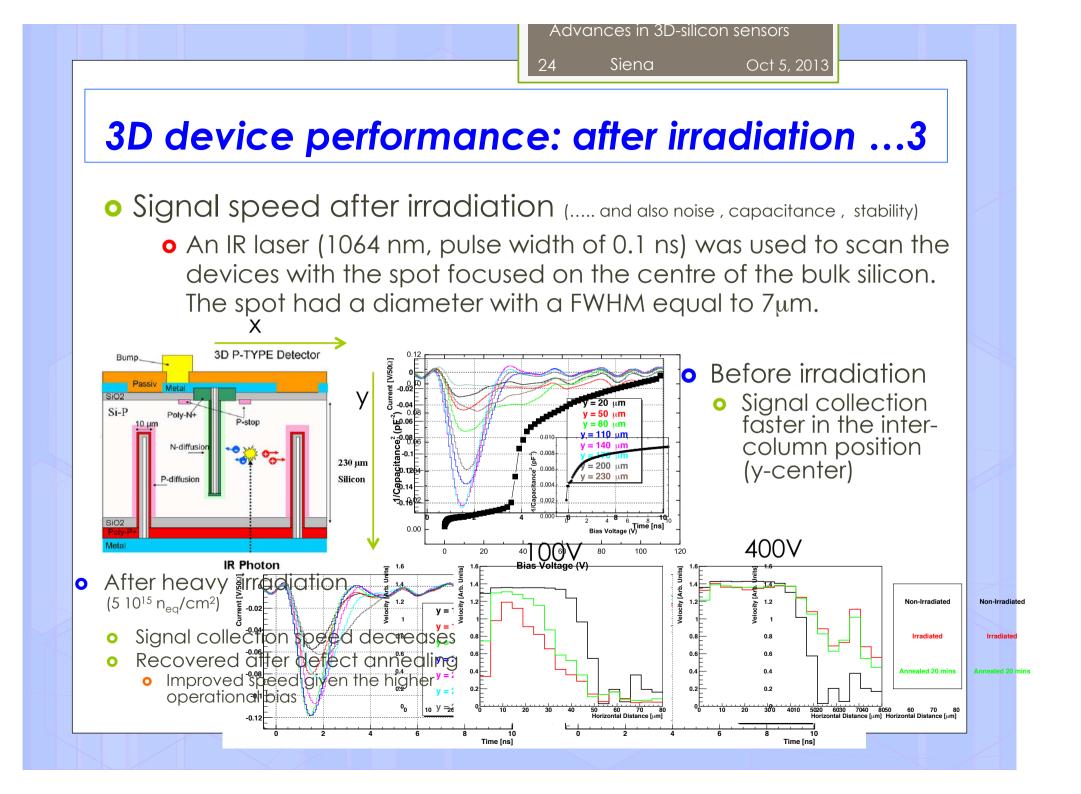

# Signal Efficiency and Signal Charge in 3D structures

January 2009

21<sup>s†</sup>

Cinzia Da Via'-The University of Manchester-SLAC -ADS-

Trapping times from Kramberger et al. NIMA 481 (2002) 100 NIM A 501(2003) 138 (Vertex 2001)

W9 - SD4

W19 - SD2

W19 - SD3

W21 - SD2 - SD3 W21

W24 - SD2

W24 - SD3

W24 - SD4

Reverse voltage [V]

- SD1

70

40

150

125

100

75

50

25

Current [nA]

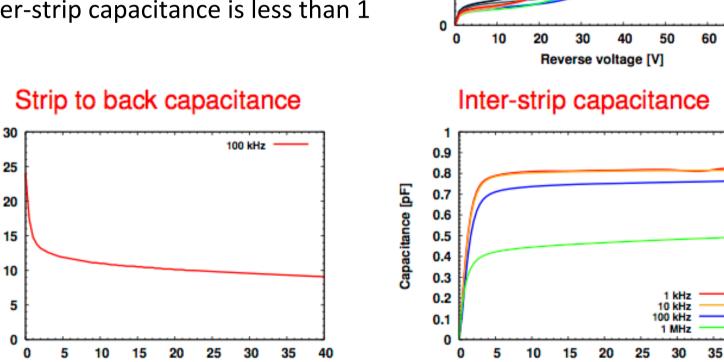

# Electrical Characterization: IV, CV

Good leakage current with • breakdown at about 40 V

Capacitance [pF]

- Strip to backplane capacitance indicates full depletion is reached at about 5 V

- Inter-strip capacitance is less than 1 • pF

Reverse voltage [V]

and 7 junction (n) columns per pixel respectively.

End of

column

ROC

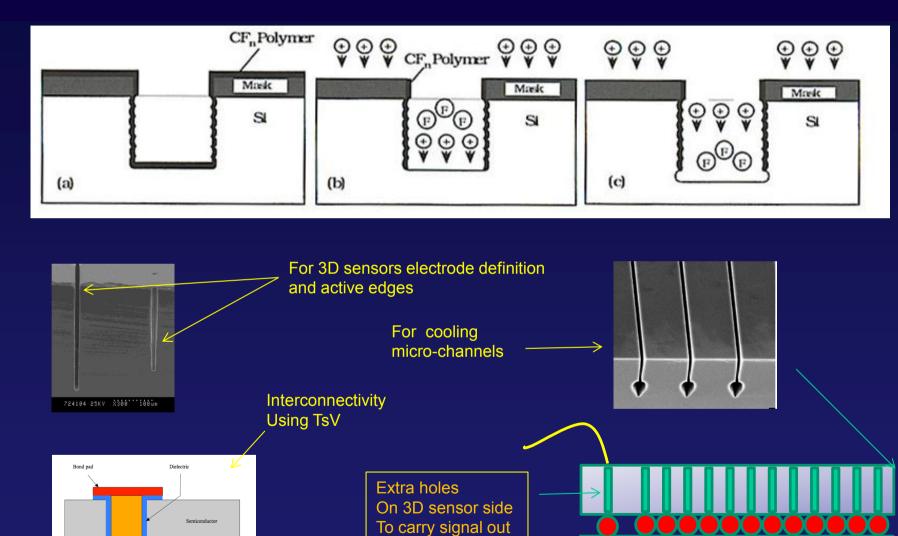

#### Microfabrication

Conductive pathway

Drawing showing the key features of a through silicon via (TSV). A TSV can be defined as "A structure that provides an electrical pathway through the thickness of a semiconductor (silicon) die between a bond pad on the front face and a land on the rear face. The pathway, the structure that provides and the front face and a land on the rear face. The pathway,

oond pads and lands are all electrically isolated from the semiconducto

1- conformal metal

2-doped poly (tests

encouraging

16

#### Activity at SINTEF

A. Kok, Workshop on 3D sensors and Microfabrication Systems

#### Temporary bonding - brewer science® waferbond®

Bonding device wafer to a carrier to allow processing

Through substrate patterning (eg. VIA) Patterning of through substrate structure

Similarly, sensors with active edges can have the support wafer removed when bonded to a carrier wafer, while sensors are release once the waferbond® is removed

Release of carrier wafer

Advances in 3D-silicon sensors 67 Siena Oct 5, 2013 3D detectors: Excavating the holes Laser Drilling Electrochemical Dry Etching etching \$618' 82849 6KV X708 > Any material > Standard photolithography process > No photolithography >No sidewall damage Slow process for big arrays ≻Sidewall damage ➤ Tapering >Sidewall damage >Si only (GaAs and SiC?) ➢ Repeatability Si and GaAs only Complex photolithography 1 hole / 3-5sec.  $1 \mu m / min.$  $0.6\mu m/min.$ Hole depth/diameter: ~ 25 Hole depth/diameter ~ 26 Hole depth/diameter: ~ 40 (but )